Université

Jean Monnet

Saint-Étienne

N° d'ordre NNT : 2025STET0011

**THÈSE de DOCTORAT

DE L'UNIVERSITÉ JEAN MONNET SAINT-ÉTIENNE**

**Membre de l'Université de Lyon**

**Ecole Doctorale N°488

SIS - Sciences Ingénierie Santé**

**Spécialité de doctorat : Microélectronique**

Soutenue publiquement le 3 février 2025, par :

**Paul GRANDAMME**

---

**Techniques avancées d'attaques par injection de fautes sur circuits intégrés**

---

Devant le jury composé de :

|                                                                                      |                    |

|--------------------------------------------------------------------------------------|--------------------|

| Sylvain GIRARD, Professeur des universités, Université Jean Monnet Saint-Etienne IUF | Président          |

| Giorgio DI NATALE, Directeur de recherche, CNRS                                      | Rapporteur         |

| Jérémy POSTEL-PELLERIN, Maître de conférences HDR, Aix-Marseille Université          | Rapporteur         |

| Vincent POUGET, Chargé de recherche, CNRS                                            | Examinateur        |

| Stéphanie ANCEAU, Ingénierie de recherche, CEA                                       | Examinateur        |

| Lilian BOSSUET, Professeur des universités, Université Jean Monnet Saint-Etienne     | Directeur de thèse |

| Jean-Max DUTERTRE, Professeur des universités, Ecole des Mines de Saint-Étienne      | Directeur de thèse |

| Michel AGOYAN, Ingénieur, STMicroelectronics                                         | Invité             |

# Remerciements

Ce manuscrit est la finalité de trois années de thèse et plus largement d'un parcours scolaire que je n'aurais pas pu mener à bien sans l'accompagnement de nombreuses personnes. À vous, ces premières pages sont dédiées.

Tout d'abord, je tiens à remercier mes directeurs de thèse, Lilian et Jean-Max pour la confiance qu'ils m'ont accordée afin de mener à bien ce projet. Jean-Max est le professeur qui a su me faire apprécier l'électronique dès mes premiers pas en école d'ingé jusqu'à ce qu'il devienne un choix de carrière. Lilian m'a accueilli dans son équipe au laboratoire pendant le COVID et m'a fait découvrir le monde de la recherche académique. Ils ont tous les deux joué un rôle déterminant dans mon choix d'orientation professionnelle. Je ne les remercierai jamais assez pour leur accompagnement ainsi que la confiance, la sympathie et la pédagogie qu'ils ont témoignées envers moi durant ces quelques années.

Plus généralement, je tiens à remercier toute l'équipe SESAM qui m'a accueillie dans un premier temps en CDD puis en thèse : Florent avec qui j'ai apprécié les nombreuses discussions cinématographiques et qui m'a fait découvrir la loi de poisson-binomiale, Pierre-Louis qui m'a donné le goût du trail et avec qui j'ai pris plaisir à donner mes enseignements, Viktor et ses anecdotes partagées la plupart du temps autour d'une bière, Vincent et son humour souvent *piquant*, Brice pour toute l'aide et les conseils qu'il m'a apportés mais aussi pour les séances de montée d'escaliers du Crêt de Roc un peu douloureuses, Nathalie qui répond toujours présente pour résoudre les problèmes, Alain qui m'a beaucoup appris sur la conception d'ASIC lors de mon CDD, Cédric avec qui j'ai pris plaisir à débriefer les matchs de l'ASSE, Damien qui m'a communiqué son expérience de doctorant dès mon arrivée dans l'équipe, Pierre-Antoine et Éloïse les rouchons : j'ai eu la chance de vous rencontrer et vous compte désormais parmi mes proches amis, Arturo et sa bonne humeur permanente, Jorge qui m'a permis d'atteindre le Top 8 (pour l'instant) du tour de Montaud, Mathieu *a.k.a* le magicien flutiste, Matéus, Raphaële, Nicolas, Anis, Simon, Alexandre, William, Viet-Sang, Justine. Je n'oublie pas les stagiaires que j'ai eu la chance d'encadrer lors de ma thèse : Émilie et Bilel.

Je remercie aussi l'ensemble des membres du département SAS de l'École des Mines de Saint-Étienne à Gardanne pour leur accueil et leurs nombreux conseils sur les parties

expérimentales de cette thèse. Je pense notamment à Raphael V, Simon, Pierre-Alain, Jean-Baptiste, Olivier, Anne-Lise ainsi qu'aux aux doctorants, Élise, Kévin, Raphaël J, Roukoz, Rodrigo et le meilleur pour la fin, Théophile.

Cette thèse a été réalisée dans le cadre du projet POP dont je tiens à remercier l'ensemble des membres : Giorgio Di Natale, Ioana Vatajelu, Paolo Maistri, David Hely, Vincent Beroulle et Aghiles Douadi. J'ai ainsi pleinement pu profiter de leurs diverses expériences lors des nombreuses réunions de projet.

Je tiens également à avoir un mot pour l'ensemble des personnels techniques et administratifs du laboratoire Hubert Curien et du campus Georges Charpak sans qui le bon déroulement de cette thèse n'aurait pas été possible.

Un grand merci à Sylvain Girard, Adriana Morana, Arnaud, Martin, Hugo de l'équipe MO-PERE du laboratoire Hubert Curien, Stéphanie Anceau, Sophie Bouat, Laurent Maingault du CEA et Luc Salvo du SIMAP pour leur collaboration scientifique dans ces travaux.

Je remercie aussi l'ensemble de la communauté de la sécurité matérielle que j'ai pu rencontrer lors de nombreux événements. Les remarques, questionnements et discussions issus de ces rencontres ont permis de faire évoluer ma recherche.

Merci également à l'ensemble de mes amis. Je vais procéder par ordre chronologique. Tout d'abord, Amélie, qui m'accompagne depuis le début du lycée. D'une rencontre un peu hasardeuse à la Base Nature de Fréjus en seconde, s'est construit une amitié qui m'est très chère aujourd'hui. Gaby et Matthieu, qui ont toujours été présents malgré la distance et nos parcours différents. Maxime, qui m'a énormément aidé, scolairement et moralement, pendant la prépa, et avec qui je prends un grand plaisir à courir la nuit entre Sainté et Lyon ou à parcourir les terrasses de bars à Lille en plein hiver. Je pense également à Louise a.k.a mon soleil musical, Hugo qui tient à nous recruter à Cambridge, Zicca que je n'ai jamais manqué de voir à Marseille lors de mes séjours à Gardanne, David et son jeu du lieu, Paul, Loïc et sa bonne humeur légendaire et Alex qui avait des cheveux à l'époque. Je remercie également mes amis stéphanois, Jérémy, Kévin, Clément, Juju, Alex, Perrine, Amandine et Léonie. C'est avec un grand plaisir que j'ai passé ces quelques années à vos côtés. J'ai aussi une pensée pour Mariane, sans qui je ne me serai sûrement pas lancé dans l'aventure d'une thèse.

Je tiens, enfin, à remercier l'ensemble de ma famille, et tout particulièrement, Pierre et Valérie. Vous m'avez montré un soutien sans faille pendant toutes ces années, depuis la première réunion parents-profs (transformée en réunion *tata-prof*) de classe prépa à ma soutenance de thèse. Je n'oublierai jamais les nombreux week-ends où vous m'avez accueilli pendant la prépa, les carnavaux de Dunkerque, les sorties à Calais-Nord ou

les vacances d'été passées avec vous. Pour tout ces moments riches, je vous remercie. Je n'oublie pas Thomas, Dominique et Margot, qui m'ont réservé un accueil privilégié pendant la prépa. Vous avez, vous aussi, largement contribué à ma réussite lors de ces années.

Un dernier remerciement à mes parents, Yves et Sylvie, et à mes frères, Gauthier et Jérôme. Vous m'avez encouragé tout au long de ce parcours scolaire et donné les moyens de le mener à bien sereinement, votre soutien sans faille m'a été précieux.

# Résumé

La sécurité physique des circuits intégrés est souvent évaluée en menant des attaques qui exploitent leurs vulnérabilités matérielles. Les attaques par injection de fautes sont une technique couramment utilisée dans cet objectif d'évaluation. Elles permettent à un attaquant d'altérer le fonctionnement nominal du composant afin d'obtenir des informations confidentielles. Les techniques principales d'injection de fautes localisées sont les injections laser et électromagnétique. Plus récemment, des travaux pionniers ont montré que les rayons X pouvaient également modifier le comportement d'un circuit. L'objectif de cette thèse est d'évaluer le potentiel des attaques en fautes. Cela se fait en améliorant l'état de l'art existant, notamment sur les attaques par injection de fautes laser et rayons X, sur des mémoires Flash de microcontrôleurs dédiés à des applications IoT. La finalité de cette étude est de contribuer à la prise en compte de la menace que constituent ces attaques mais également de comprendre les phénomènes associés. Ces points constituent les premiers pas en vue de la conception de contre-mesures adaptées. Premièrement, après une description des limitations des bancs laser monospot, nous caractérisons les avantages significatifs, notamment d'un point de vue spatial et temporel, apportés par un nouveau banc laser multispot. Des exemples concrets de scénarios désormais atteignables sont décrits et une exploration théorique des nouvelles possibilités offertes par le banc laser est également réalisée. Deuxièmement, nous mettons en lumière la possibilité d'utiliser l'effet thermique d'un banc laser infrarouge afin d'injecter des fautes persistantes au sein de mémoires Flash de composants non alimentés. Ce nouveau vecteur d'attaque aboutit à la description d'un nouveau modèle de faute complet allant du niveau physique au niveau applicatif. Les résultats obtenus nous permettent d'une part, de réaliser l'ingénierie inverse de la mémoire Flash du composant ciblé et d'autre part, de retrouver la clé de chiffrement d'une implémentation logicielle de l'algorithme de chiffrement AES. Pour finir, l'utilisation de sources non focalisées de rayons X est décrite dans le but d'injecter des fautes dans des mémoires Flash de composants alimentés et non alimentés. Les phénomènes de récupération thermique et temporelle sont également caractérisés. La conception et la caractérisation de masques permettant, dans une certaine mesure, de focaliser l'injection de fautes est mise en pratique.

## Abstract

The security of integrated circuits is evaluated through the implementation of attacks that exploit their inherent hardware vulnerabilities. Fault injection attacks represent a technique that is commonly employed for this purpose. These techniques permit an attacker to alter the nominal operation of the component in order to obtain confidential information. The principal techniques for localised fault injection are laser and electromagnetic injection. Recently, pioneering work has demonstrated that X-rays can also modify the behaviour of a circuit. The objective of this thesis is to assess the potential of fault attacks. This is achieved by advancing the existing state of the art, with a particular focus on laser and X-ray fault injection attacks on Flash memories of microcontrollers dedicated to the IoT. The aim of this study is twofold : firstly, to highlight the threat posed by these attacks and secondly, to gain insight into the associated mechanisms. These steps are crucial for the development of effective countermeasures. Firstly, after outlining the limitations of single-spot laser benches, we present a detailed analysis of the significant advantages offered by a new multispot laser bench, particularly in terms of spatial and temporal capacity. The study goes on to describe a number of concrete examples of scenarios that are now achievable, and also carries out a theoretical exploration of the new possibilities offered by the laser bench. Secondly, we propose the utilisation of the thermal effect of an infrared laser bench for the injection of persistent faults into the Flash memory of unpowered components. This novel attack vector gives rise to the delineation of a comprehensive new fault model, encompassing both the physical and application levels. The outcomes obtained facilitate the reverse engineering of the Flash memory of the targeted component and the extraction of the encryption key for a software implementation of the AES encryption algorithm. The final section of the thesis describes the use of unfocused X-ray sources for the injection of faults into the Flash memories of both powered and unpowered components. Furthermore, the thermal and temporal recovery phenomena are also characterised. The design and characterisation of masks that enable the focused injection of faults are demonstrated.

# Table des matières

---

|                                                       |      |

|-------------------------------------------------------|------|

| <b>Remerciements</b>                                  | iii  |

| <b>Résumé</b>                                         | vii  |

| <b>Liste des figures</b>                              | xvii |

| <b>Liste des tableaux</b>                             | xix  |

| <b>Liste des sigles</b>                               | xxi  |

| <b>1 Introduction générale</b>                        | 1    |

| 1.1 Positionnement du problème . . . . .              | 1    |

| 1.2 Plan et contributions . . . . .                   | 4    |

| 1.3 Contexte . . . . .                                | 5    |

| <b>2 Notions préliminaires</b>                        | 7    |

| 2.1 Introduction . . . . .                            | 8    |

| 2.2 Technologie MOS . . . . .                         | 8    |

| 2.3 Mémoires volatiles . . . . .                      | 9    |

| 2.4 Mémoires non volatiles . . . . .                  | 10   |

| 2.4.1 Transistor à grille flottante . . . . .         | 11   |

| 2.4.2 Mémoires Flash . . . . .                        | 15   |

| 2.5 Chiffrement AES . . . . .                         | 16   |

| 2.6 Attaques par injection de fautes . . . . .        | 19   |

| 2.6.1 Classification des fautes matérielles . . . . . | 20   |

| 2.6.2 Modèle de fautes . . . . .                      | 20   |

| 2.6.3 Conséquences au niveau de la mémoire . . . . .  | 21   |

| 2.7 Scénarios d'attaque . . . . .                     | 22   |

| 2.8 Mécanisme de protection . . . . .                 | 26   |

| <b>3 État de l'art</b>                                | 29   |

| 3.1 Introduction . . . . .                            | 30   |

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| 3.2      | Effet du laser sur les circuits intégrés . . . . .                      | 30        |

| 3.2.1    | Niveau physique . . . . .                                               | 30        |

| 3.2.2    | Niveau logique . . . . .                                                | 35        |

| 3.2.3    | Niveau logiciel . . . . .                                               | 39        |

| 3.3      | Effets des radiations . . . . .                                         | 40        |

| 3.3.1    | Environnements radiatifs . . . . .                                      | 41        |

| 3.3.2    | Interactions radiation-matière . . . . .                                | 44        |

| 3.3.3    | Effets des radiations sur l'électronique . . . . .                      | 48        |

| 3.4      | Effet du vieillissement . . . . .                                       | 53        |

| 3.4.1    | Instabilité de la température de polarisation . . . . .                 | 54        |

| 3.4.2    | Injection de porteurs chauds . . . . .                                  | 56        |

| 3.4.3    | Time-Dependant-Dielectric Breakdown . . . . .                           | 56        |

| 3.4.4    | Électromigration . . . . .                                              | 57        |

| 3.5      | Conclusion . . . . .                                                    | 58        |

| 3.5.1    | Objectifs de ces travaux . . . . .                                      | 58        |

| 3.5.2    | Contributions . . . . .                                                 | 58        |

| <b>4</b> | <b>Injection laser de fautes avec un banc laser multispot</b> . . . . . | <b>59</b> |

| 4.1      | Introduction . . . . .                                                  | 60        |

| 4.2      | Généralités . . . . .                                                   | 60        |

| 4.3      | Limites d'un banc laser monospot . . . . .                              | 61        |

| 4.3.1    | Limite spatiale . . . . .                                               | 61        |

| 4.3.2    | Limite temporelle . . . . .                                             | 62        |

| 4.4      | Présentation du dispositif expérimental . . . . .                       | 63        |

| 4.4.1    | Banc laser ALPhANOV . . . . .                                           | 63        |

| 4.4.2    | Cible . . . . .                                                         | 65        |

| 4.5      | Caractérisation . . . . .                                               | 69        |

| 4.5.1    | Montage expérimental . . . . .                                          | 70        |

| 4.5.2    | Réglage des sources laser . . . . .                                     | 70        |

| 4.5.3    | Programmes de test . . . . .                                            | 71        |

| 4.5.4    | Avantage spatial . . . . .                                              | 71        |

| 4.5.5    | Avantage temporel . . . . .                                             | 73        |

| 4.6      | Nouvelles possibilités d'attaques . . . . .                             | 76        |

| 4.7      | Conclusion . . . . .                                                    | 78        |

| <b>5</b> | <b>Injection laser de fautes sur circuit non alimenté</b> . . . . .     | <b>79</b> |

| 5.1      | Introduction . . . . .                                                  | 80        |

| 5.2      | Modèle de faute . . . . .                                               | 80        |

| 5.2.1    | Modèle de faute au niveau physique en mémoire Flash . . . . .           | 81        |

|          |                                                                             |            |

|----------|-----------------------------------------------------------------------------|------------|

| 5.2.2    | Modèle de faute au niveau logique en mémoire Flash . . . . .                | 84         |

| 5.2.3    | Modèle de faute au niveau mémoire Flash et niveau applicatif . .            | 85         |

| 5.3      | Validation expérimentale du modèle de faute au niveau logique . . . . .     | 86         |

| 5.3.1    | Matériel . . . . .                                                          | 86         |

| 5.3.2    | Protocole expérimental . . . . .                                            | 87         |

| 5.3.3    | Résultats . . . . .                                                         | 88         |

| 5.4      | Application . . . . .                                                       | 92         |

| 5.4.1    | Implémentation de l'attaque . . . . .                                       | 93         |

| 5.4.2    | Modèle d'attaquant en pratique . . . . .                                    | 95         |

| 5.4.3    | Amélioration de la PFA . . . . .                                            | 96         |

| 5.4.4    | Résultats expérimentaux . . . . .                                           | 98         |

| 5.5      | Discussion . . . . .                                                        | 99         |

| 5.6      | Conclusion . . . . .                                                        | 100        |

| <b>6</b> | <b>Injection par rayons X de fautes sur circuit non alimenté</b>            | <b>101</b> |

| 6.1      | Introduction . . . . .                                                      | 102        |

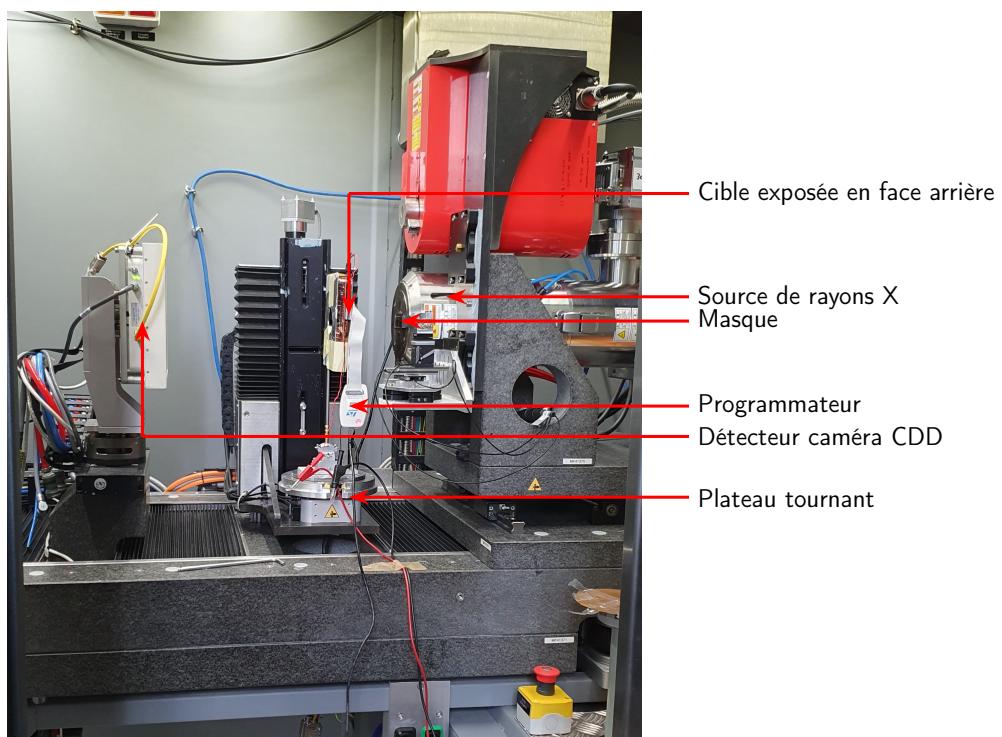

| 6.2      | Présentation du dispositif expérimental d'irradiation X . . . . .           | 102        |

| 6.2.1    | Généralités sur les sources de rayons X . . . . .                           | 102        |

| 6.2.2    | Matériel d'irradiation et cible . . . . .                                   | 104        |

| 6.2.3    | Protocole expérimental . . . . .                                            | 107        |

| 6.3      | Caractérisation de l'exposition aux rayons X d'un microcontrôleur . . . . . | 109        |

| 6.3.1    | Résultats expérimentaux des campagnes d'irradiation . . . . .               | 109        |

| 6.3.2    | Récupération temporelle et thermique . . . . .                              | 112        |

| 6.3.3    | Synthèse des résultats obtenus . . . . .                                    | 113        |

| 6.4      | Réalisation d'un masque de focalisation . . . . .                           | 115        |

| 6.4.1    | Simulations numériques de l'efficacité des masques . . . . .                | 115        |

| 6.4.2    | Caractérisation expérimentale du masque . . . . .                           | 116        |

| 6.5      | Utilisation d'un tomographe comme irradiateur . . . . .                     | 121        |

| 6.5.1    | Description du tomographe . . . . .                                         | 121        |

| 6.5.2    | Expériences réalisées . . . . .                                             | 124        |

| 6.5.3    | Synthèse des résultats . . . . .                                            | 129        |

| 6.6      | Conclusion . . . . .                                                        | 130        |

| <b>7</b> | <b>Conclusion générale</b>                                                  | <b>133</b> |

| 7.1      | Conclusion . . . . .                                                        | 133        |

| 7.2      | Perspectives . . . . .                                                      | 134        |

| 7.3      | Publications . . . . .                                                      | 136        |

| 7.3.1    | Publication dans un journal international . . . . .                         | 136        |

| 7.3.2    | Conférence internationale avec comité de lecture . . . . .                  | 136        |

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| 7.4 Communications . . . . .                                      | 136        |

| 7.4.1 Présentation à un congrès international sans acte . . . . . | 136        |

| 7.4.2 Présentation à un congrès national sans acte . . . . .      | 136        |

| 7.4.3 Posters . . . . .                                           | 137        |

| <b>Bibliographie</b>                                              | <b>139</b> |

# Liste des figures

---

|      |                                                                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Classification des attaques physiques [Bos18]. . . . .                                                                | 2  |

| 2.1  | Vue en coupe de transistors NMOS et PMOS en technologie CMOS. . . . .                                                 | 8  |

| 2.2  | Schéma électrique des transistors NMOS et PMOS. . . . .                                                               | 9  |

| 2.3  | Cellule SRAM standard à 6 transistors. . . . .                                                                        | 10 |

| 2.4  | Vue en coupe d'un transistor à grille flottante. . . . .                                                              | 11 |

| 2.5  | Tensions appliqués aux bornes d'un transistor à grille flottante pendant les différentes opérations [Vie+21]. . . . . | 12 |

| 2.6  | Programmation (a) et Effacement (b) d'un transistor à grille flottante. . . . .                                       | 12 |

| 2.7  | Caractéristique I-V de transistors à grille flottante chargé et déchargé. . . . .                                     | 13 |

| 2.8  | Lecture de transistors à grille flottante (architecture NOR). . . . .                                                 | 14 |

| 2.9  | Vue en coupe d'une mémoire NOR Flash pendant l'opération de lecture. . . . .                                          | 14 |

| 2.10 | Organisation usuelle des mémoires Flash. . . . .                                                                      | 15 |

| 2.11 | Architectures des mémoires Flash. . . . .                                                                             | 16 |

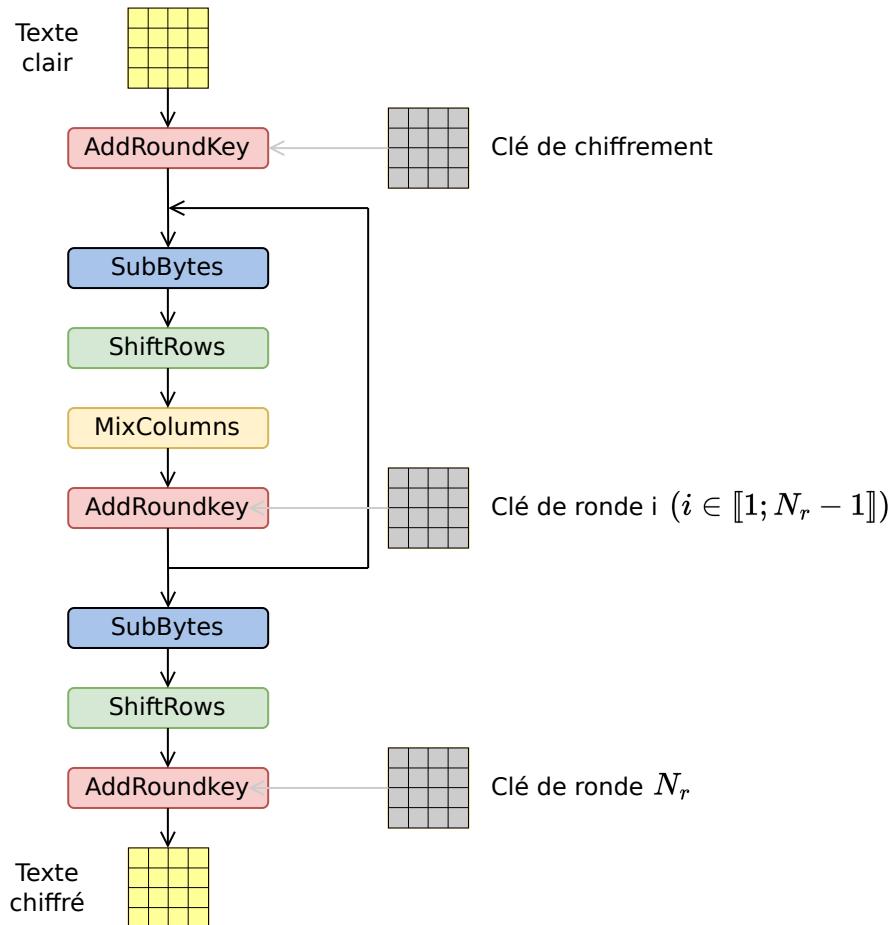

| 2.12 | Déroulement du chiffrement AES. . . . .                                                                               | 17 |

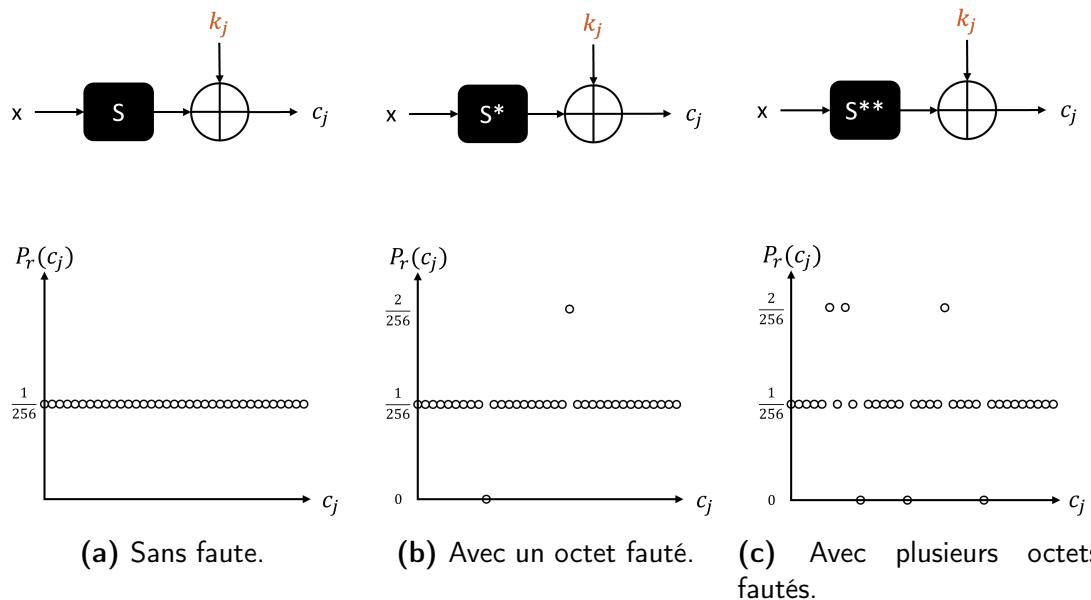

| 2.13 | Distribution de probabilité des octets du chiffré en fonction du nombre de fautes sur la S-Box (S). . . . .           | 24 |

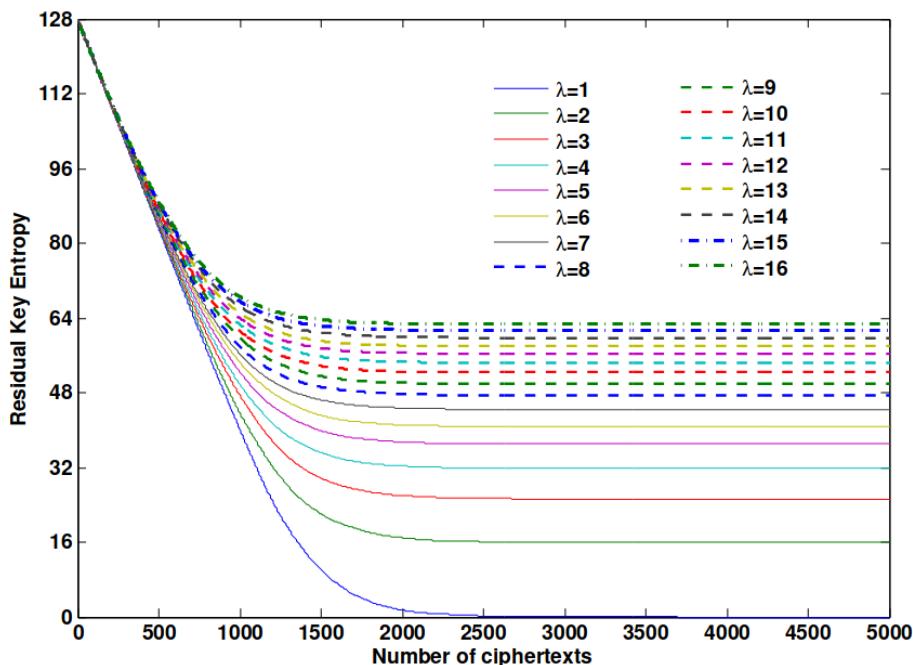

| 2.14 | Entropie résiduelle de la clé en fonction du nombre d'octets fautés et du nombre de textes chiffrés [Zha+18]. . . . . | 26 |

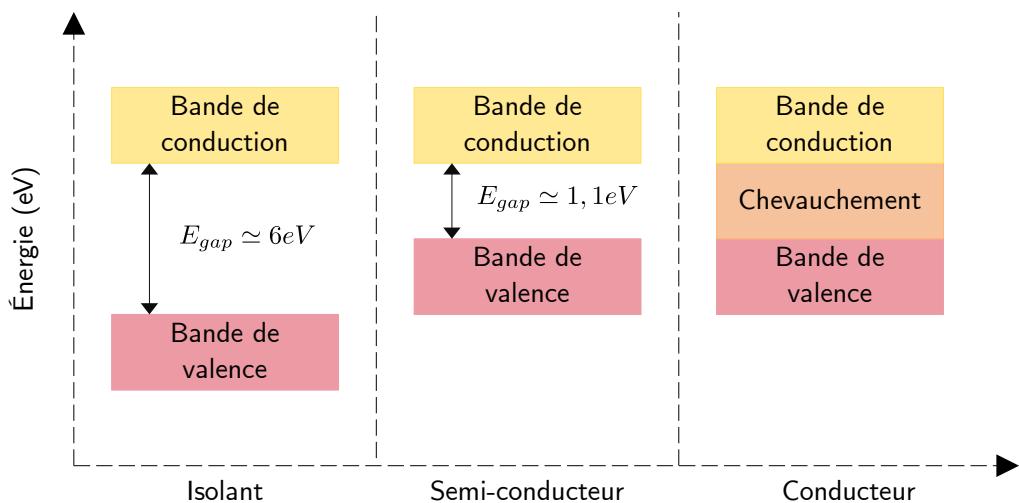

| 3.1  | Position des différentes bandes d'énergie. . . . .                                                                    | 31 |

| 3.2  | Absorption d'un photon par effet photoélectrique. . . . .                                                             | 32 |

| 3.3  | Mécanisme d'apparition d'un photocourant. . . . .                                                                     | 33 |

| 3.4  | Évolution temporelle du photocourant [Hab65]. . . . .                                                                 | 33 |

| 3.5  | Modélisation électrique d'un tir laser sur un transistor NMOS [Dou+05]. . . . .                                       | 34 |

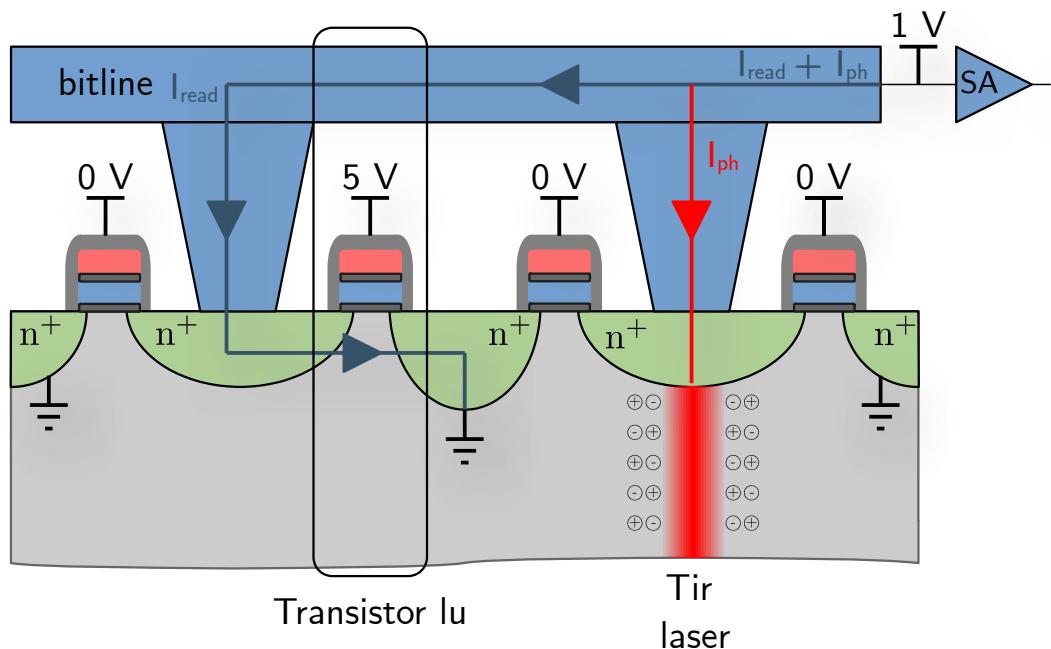

| 3.6  | Mécanisme d'apparition d'un photocourant dans une colonne d'une mémoire NOR Flash. . . . .                            | 35 |

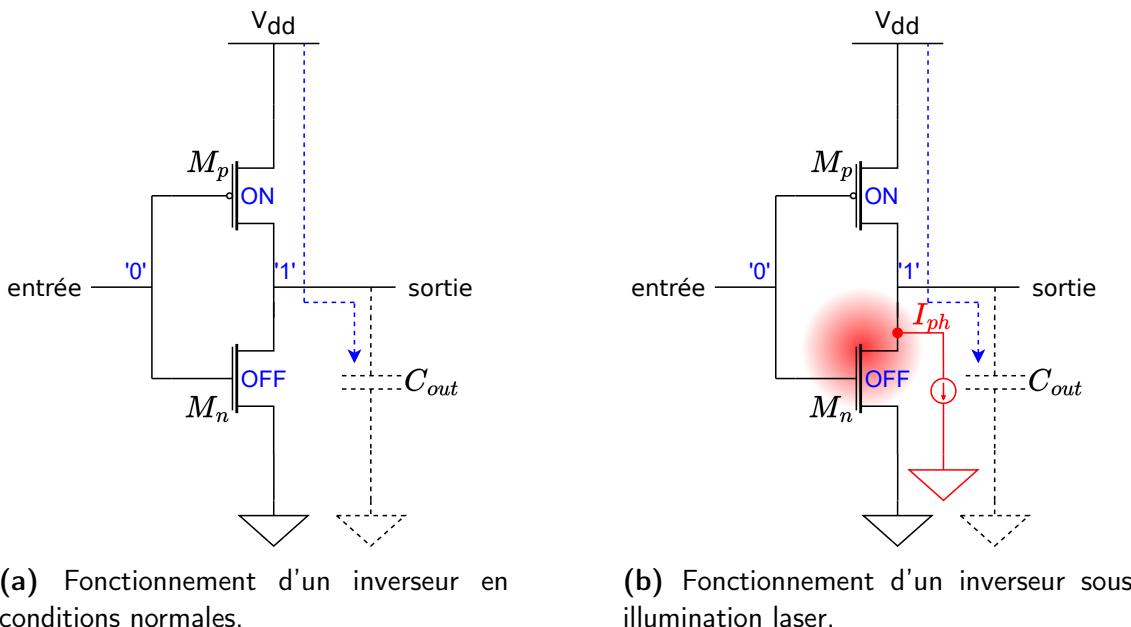

| 3.7  | Effet d'un tir laser sur un inverseur CMOS. . . . .                                                                   | 36 |

| 3.8  | Injection d'une faute sur une cellule SRAM. Le cercle rouge représente le spot laser. . . . .                         | 37 |

|      |                                                                                                                                                                                                              |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Cartographie spatiale des fautes sur la mémoire Flash d'un STM32F100RB [Men+19]. . . . .                                                                                                                     | 38 |

| 3.10 | Exemples de corruption d'instructions lors de l'opération de lecture [Col+19]. . . . .                                                                                                                       | 40 |

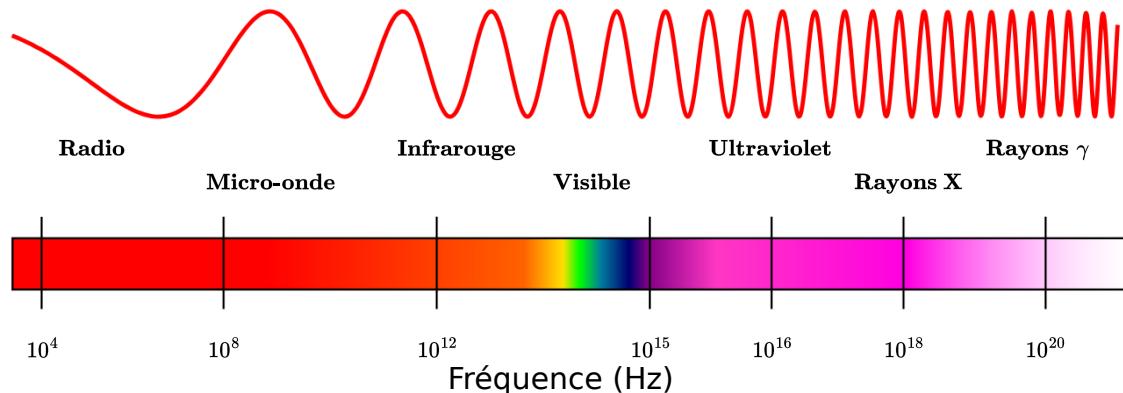

| 3.11 | Spectre électromagnétique. . . . .                                                                                                                                                                           | 41 |

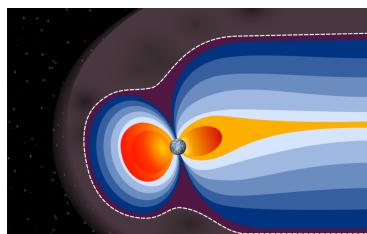

| 3.12 | Magnétosphère et ceintures de Van Allen. Source NASA/Wikimedia Commons. . . . .                                                                                                                              | 42 |

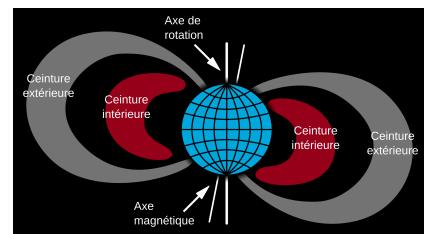

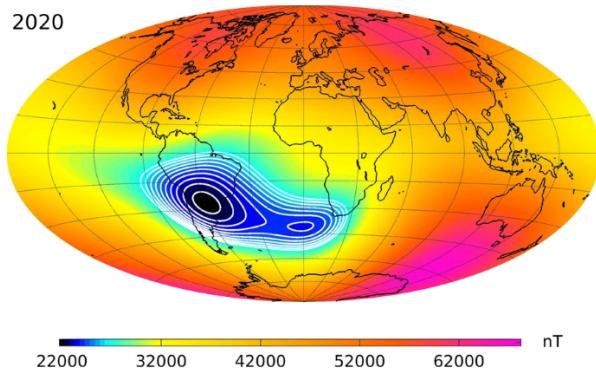

| 3.13 | Champ magnétique terrestre et anomalie de l'Atlantique sud. Source [Fin+20]. . . . .                                                                                                                         | 43 |

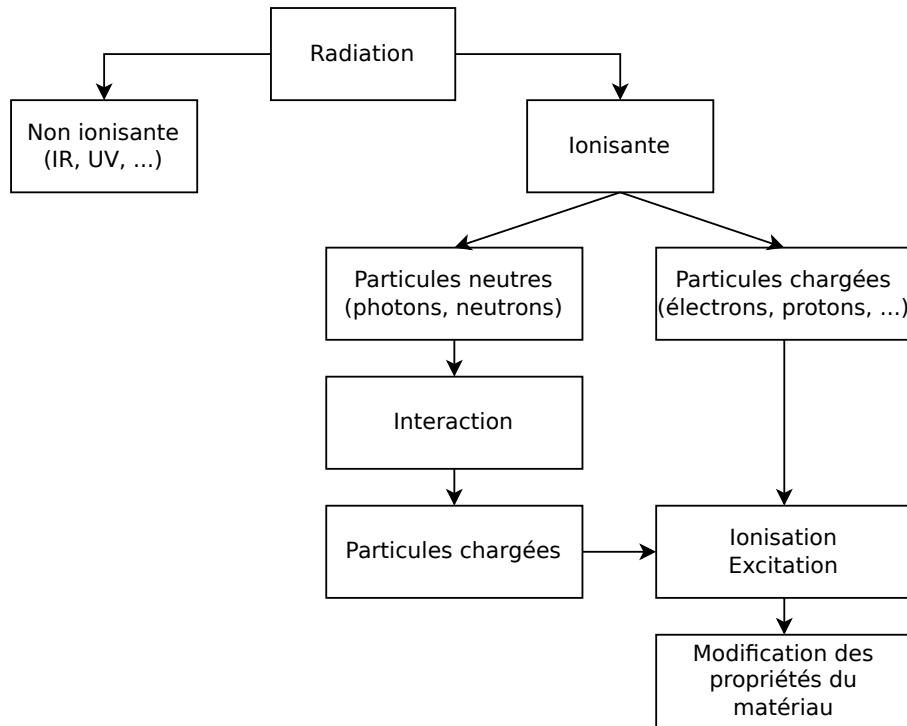

| 3.14 | Interaction radiation-matière. . . . .                                                                                                                                                                       | 45 |

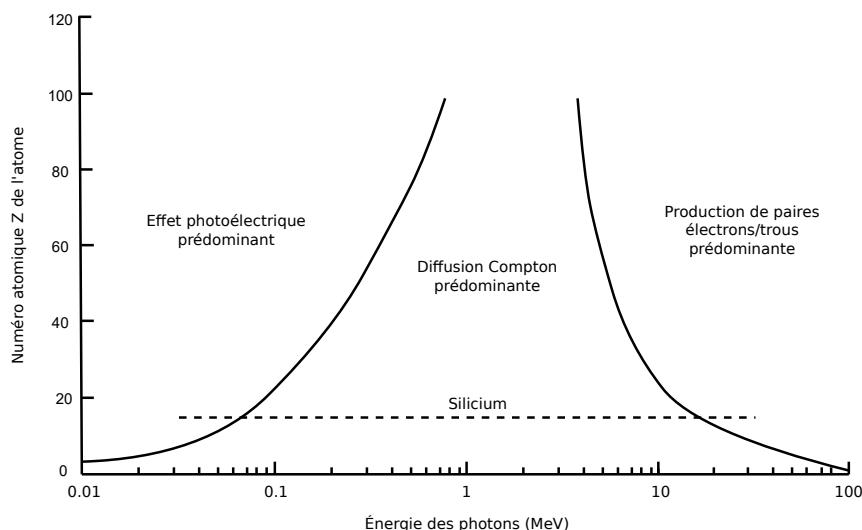

| 3.15 | Domaine de prédominance des différents effets selon l'énergie du photon incident. Adapté de [Sch94]. . . . .                                                                                                 | 47 |

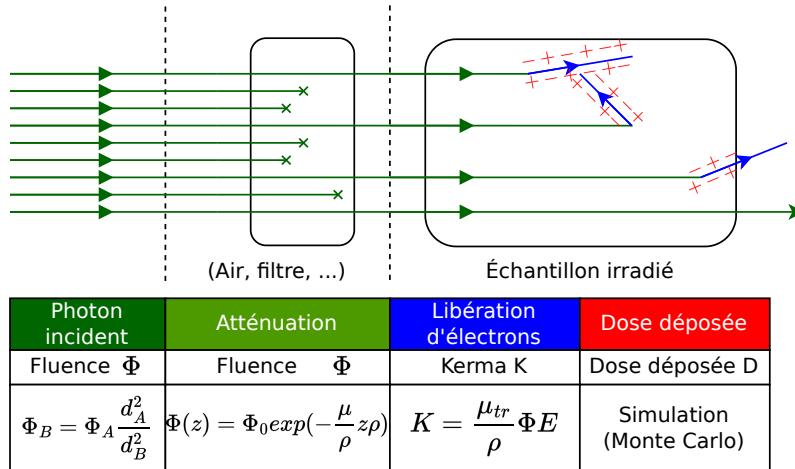

| 3.16 | Schéma de synthèse des différentes étapes avec les grandeurs physiques représentatives. [Mey23]. . . . .                                                                                                     | 48 |

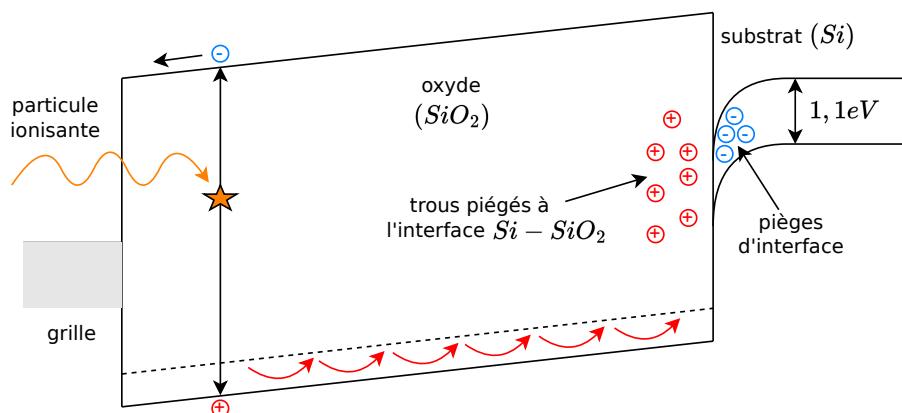

| 3.17 | Principales étapes de l'effet TID. Adaptée de [Bar06]. . . . .                                                                                                                                               | 49 |

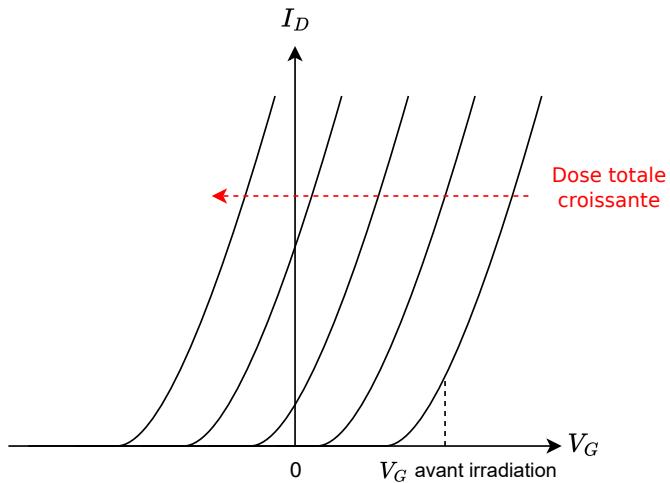

| 3.18 | Effet de la totale sur la caractéristique $I_D = f(V_{GS})$ d'un transistor NMOS. Adaptée de [Sha02]. . . . .                                                                                                | 50 |

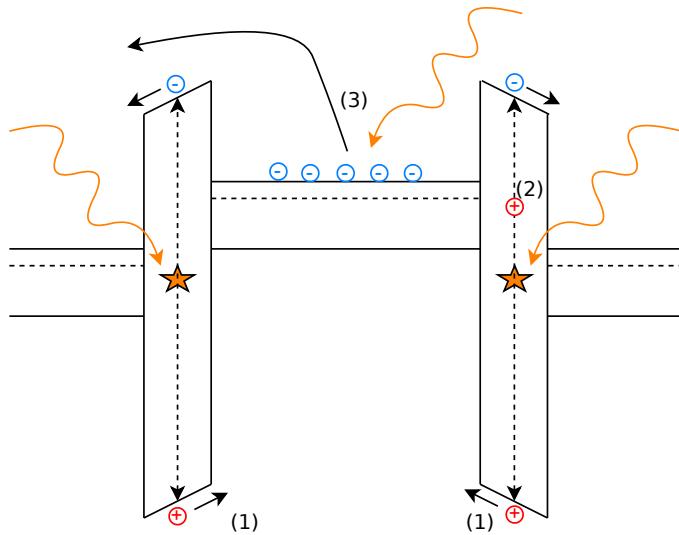

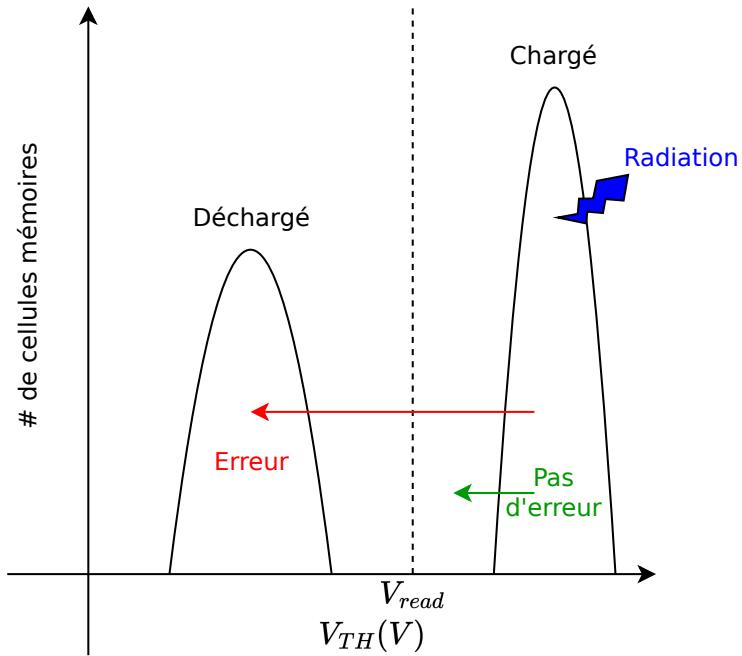

| 3.19 | Mécanismes TID dans un transistor à grille flottante. Adaptée de [Ger+13]. . . . .                                                                                                                           | 51 |

| 3.20 | Impact des radiations sur la distribution des tensions de seuil des transistors à grille flottante d'une mémoire Flash. Adaptée de [Ger+13]. . . . .                                                         | 52 |

| 3.21 | Vue en coupe d'un inverseur CMOS avec la structure <i>pnpn</i> parasite. . . . .                                                                                                                             | 54 |

| 3.22 | Configuration électrique d'une contrainte NBTI. . . . .                                                                                                                                                      | 55 |

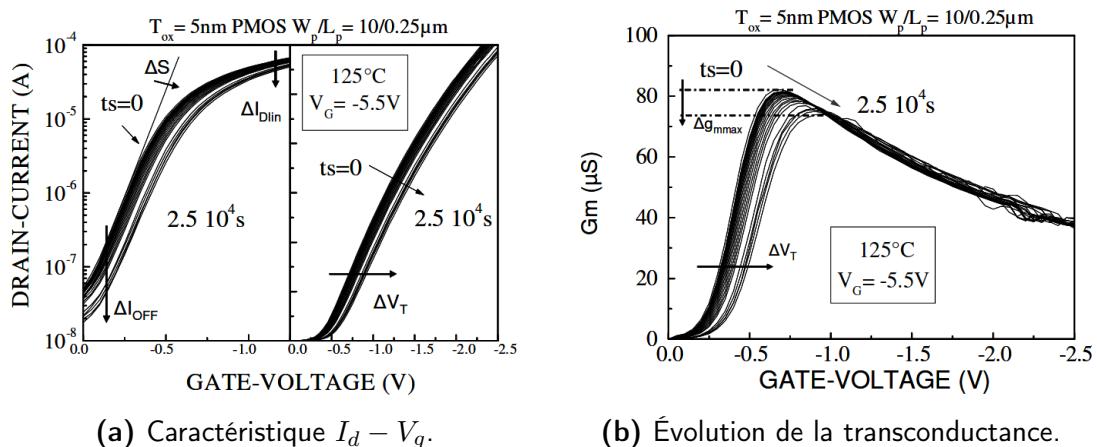

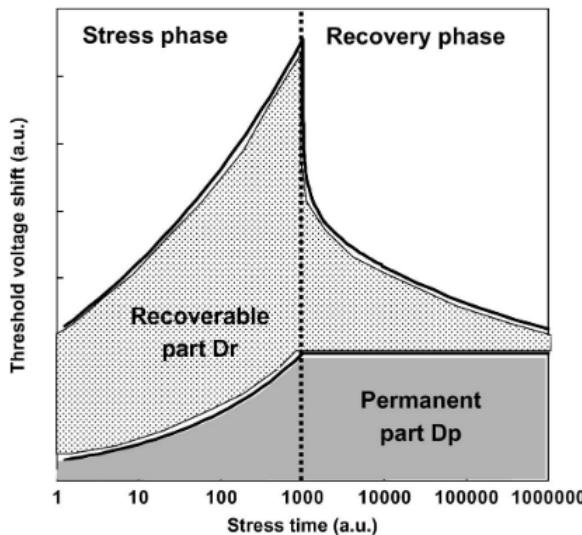

| 3.23 | Dérive des paramètres électriques d'un transistor PMOS après une contrainte NBTI. [Den05]. . . . .                                                                                                           | 55 |

| 3.24 | Illustration des effets permanents et recouvrables de la contrainte NBTI sur la tension de seuil. [Hua+07]. . . . .                                                                                          | 56 |

| 3.25 | Injection d'électrons chauds dans un NMOS. . . . .                                                                                                                                                           | 57 |

| 3.26 | Différents types de TDDB au sein d'un composant. . . . .                                                                                                                                                     | 57 |

| 4.1  | Faisabilité de fautes multi-bits contiguë et non contiguë avec un seul spot laser. . . . .                                                                                                                   | 62 |

| 4.2  | Faisabilité de fautes consécutives avec un seul spot ou plusieurs spots laser sur un mot de 32 bits. . . . .                                                                                                 | 63 |

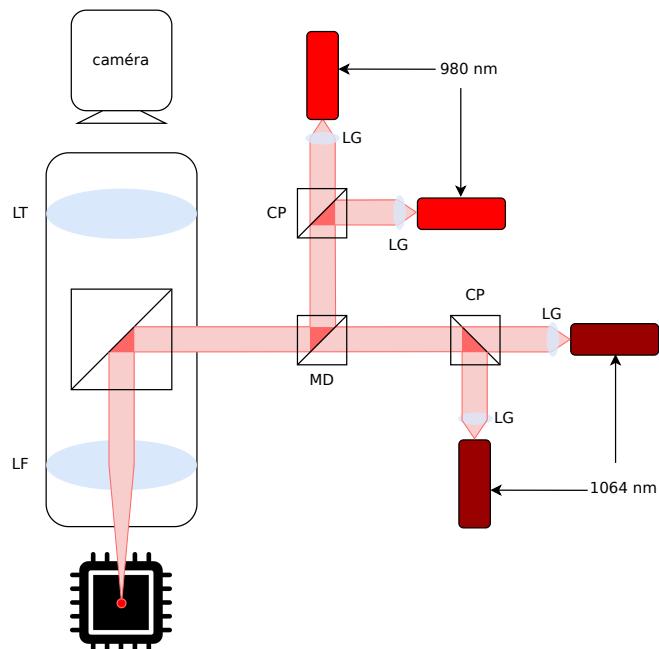

| 4.3  | Schéma du banc laser à quatre spots. (CP : Cube séparateur de faisceau de Polarisation, MD : Miroir Dichroïque, LF : Lentille de Focalisation, LG : Lentille Grossissante, LT : Lentille Tubulaire). . . . . | 64 |

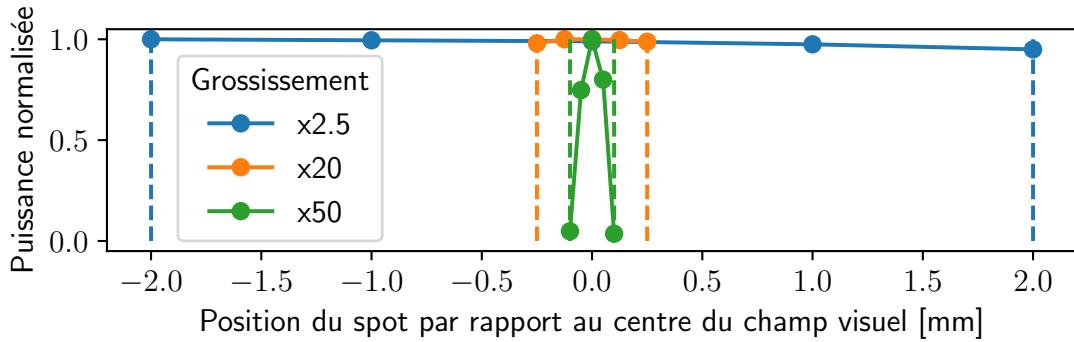

| 4.4  | Puissance relative du laser en fonction de la distance entre le spot et le centre de l'objectif. . . . .                                                                                                     | 66 |

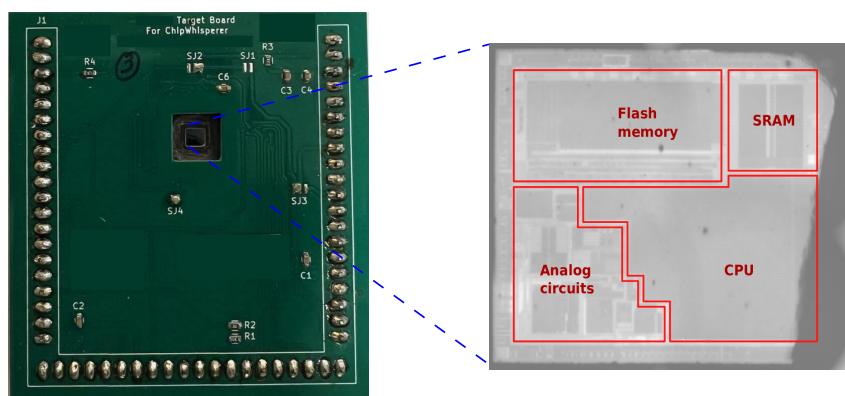

| 4.5  | Carte de test (gauche) et image infrarouge (droite) de la cible. . . . .                                                                                                                                     | 67 |

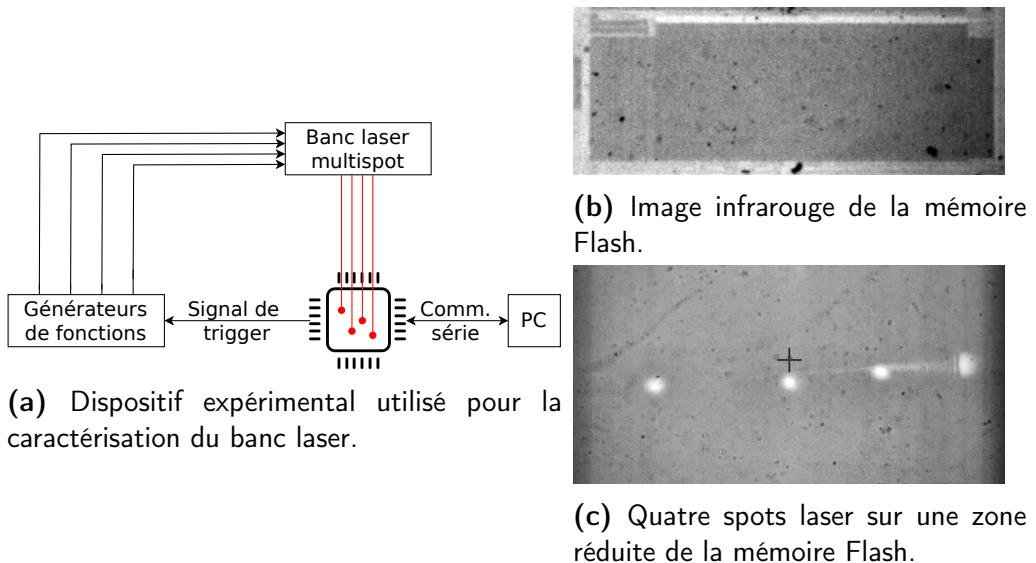

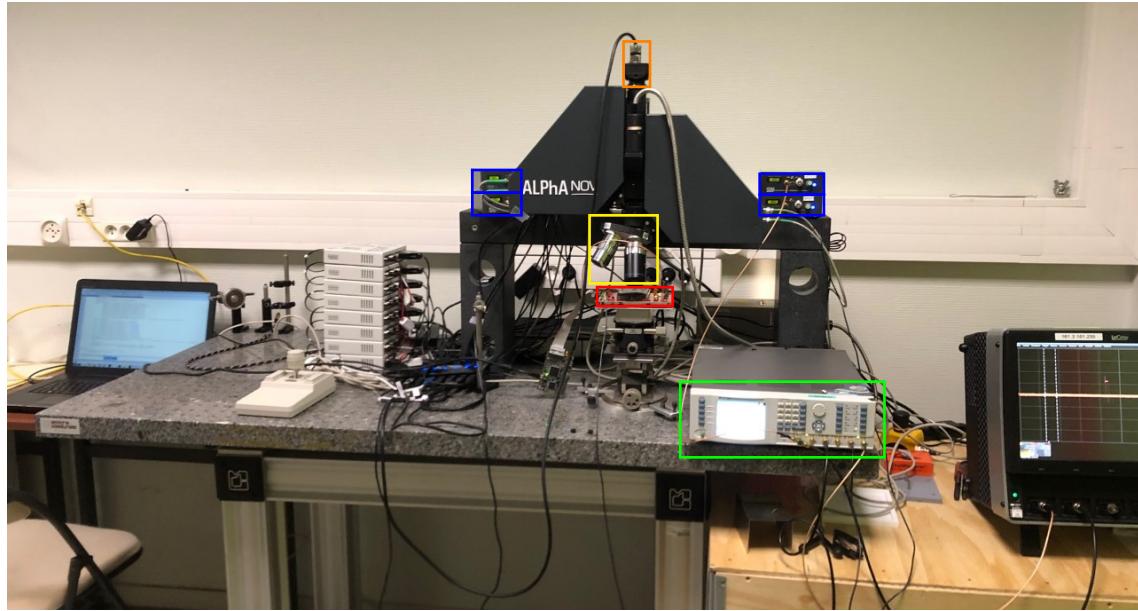

| 4.6  | Injection laser à quatre spots sur une mémoire Flash. . . . .                                                                                                                                                | 70 |

|      |                                                                                                                                                               |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.7  | Photographie du montage expérimentale de caractérisation du banc laser multispot. . . . .                                                                     | 71  |

| 4.8  | Code assembleur de caractérisation pour quatre fautes simultanées sur des bits non contigus. . . . .                                                          | 72  |

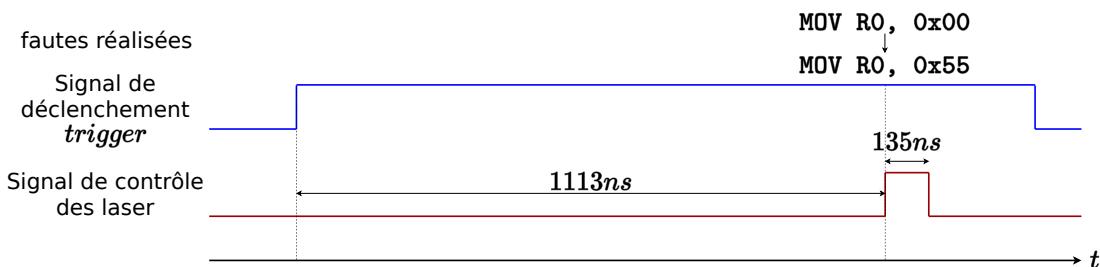

| 4.9  | Chronogramme de la caractérisation de l'avantage spatial . . . . .                                                                                            | 72  |

| 4.10 | Code de caractérisation pour deux fautes proches dans le temps sur des bits d'indice différent. . . . .                                                       | 73  |

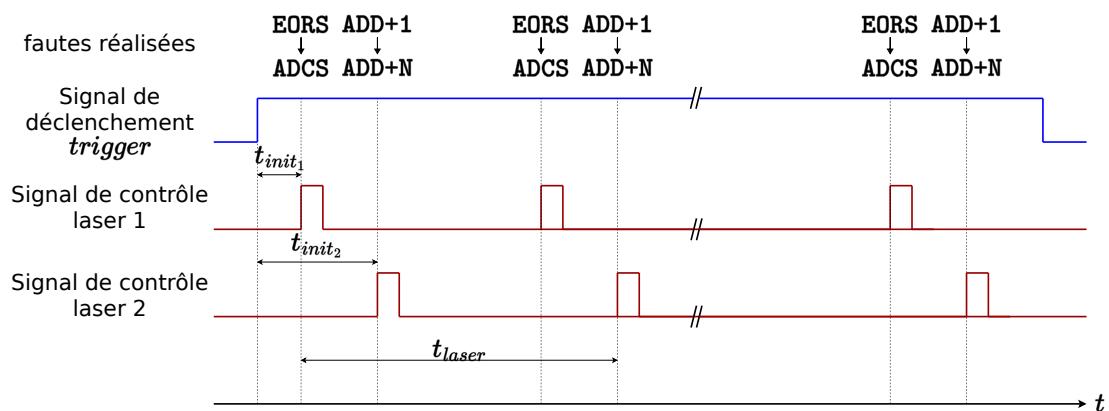

| 4.11 | Évolution temporelle des différents signaux de contrôle. . . . .                                                                                              | 75  |

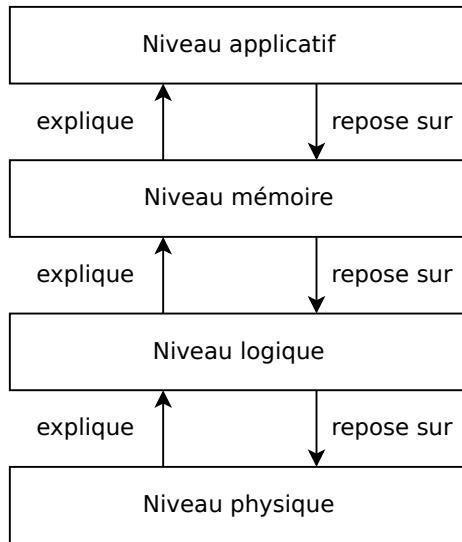

| 5.1  | Représentation schématique des liens entre les différents niveaux d'abstraction d'un modèle de faute. . . . .                                                 | 81  |

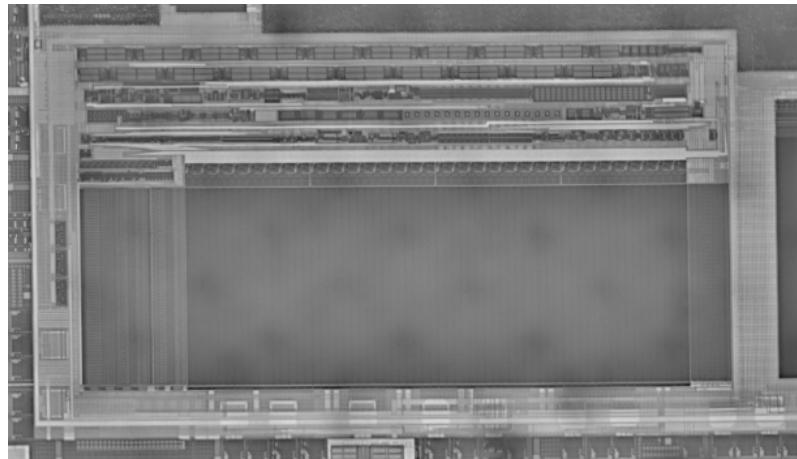

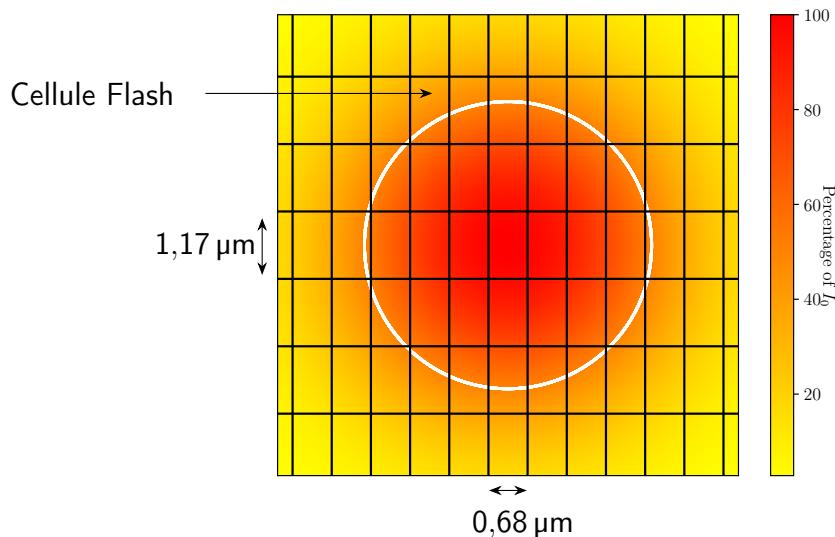

| 5.2  | Image infrarouge de la mémoire Flash. . . . .                                                                                                                 | 83  |

| 5.3  | Carte thermique générée par l'exposition laser avec l'objectif $\times 20$ (Simulation numérique avec $\lambda = 1\,064\,\text{nm}$ et $NA = 0,16$ ). . . . . | 83  |

| 5.4  | Modèle de faute au niveau physique et logique. . . . .                                                                                                        | 84  |

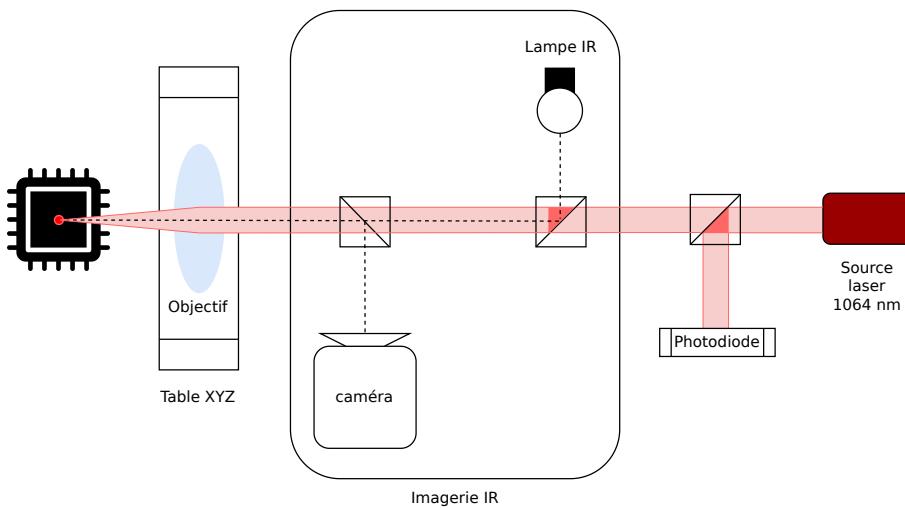

| 5.5  | Schéma du banc laser Pulscan [Pul24]. . . . .                                                                                                                 | 86  |

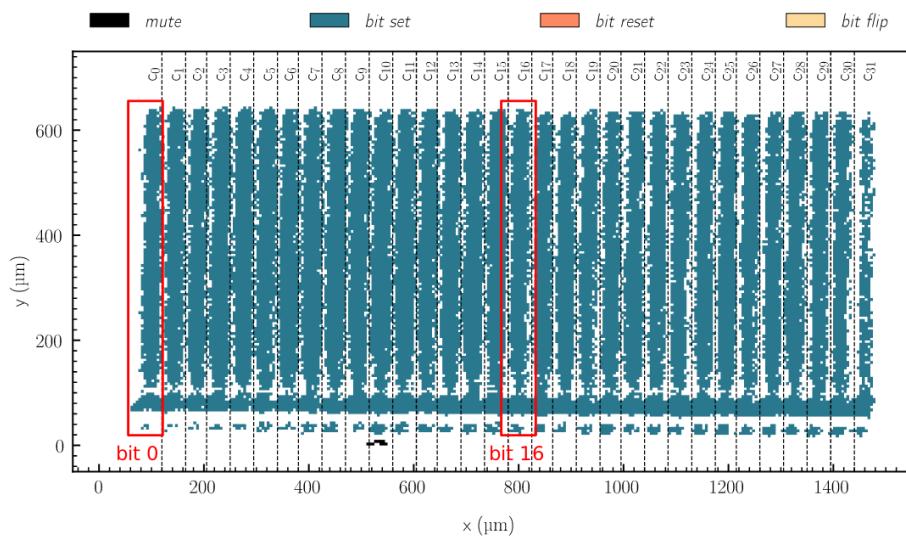

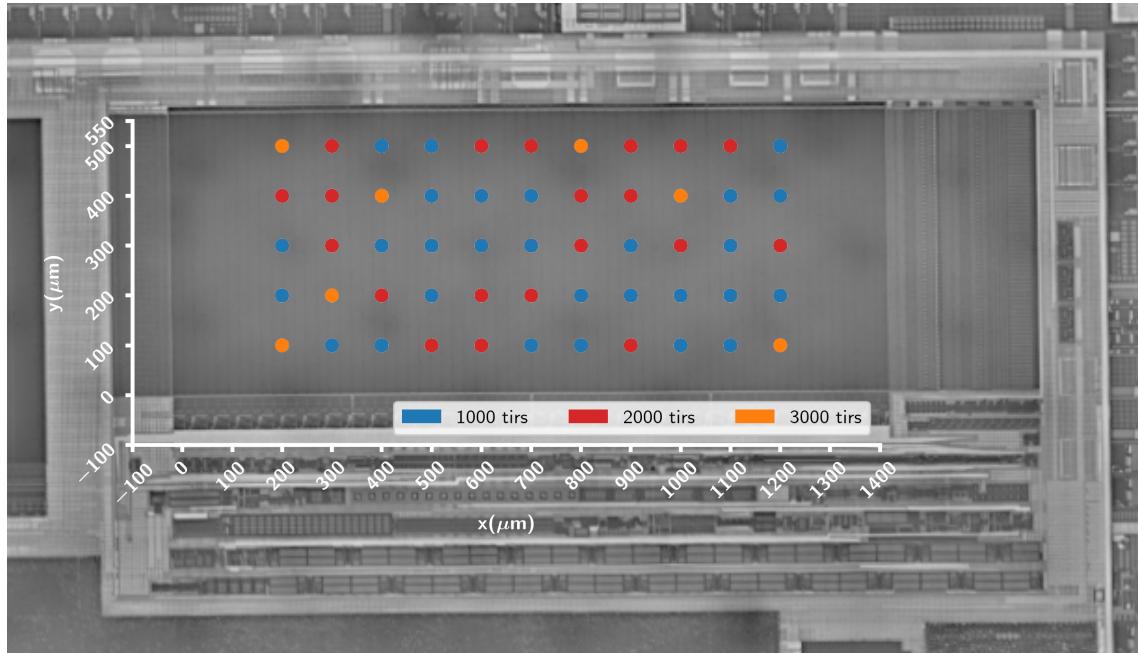

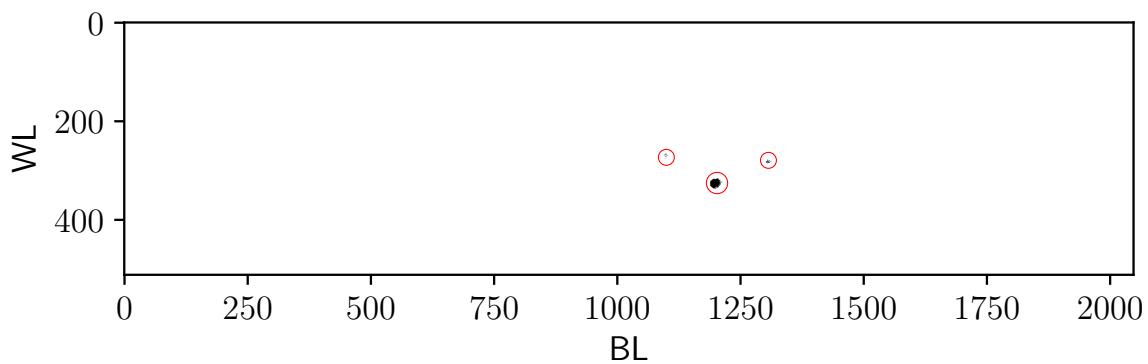

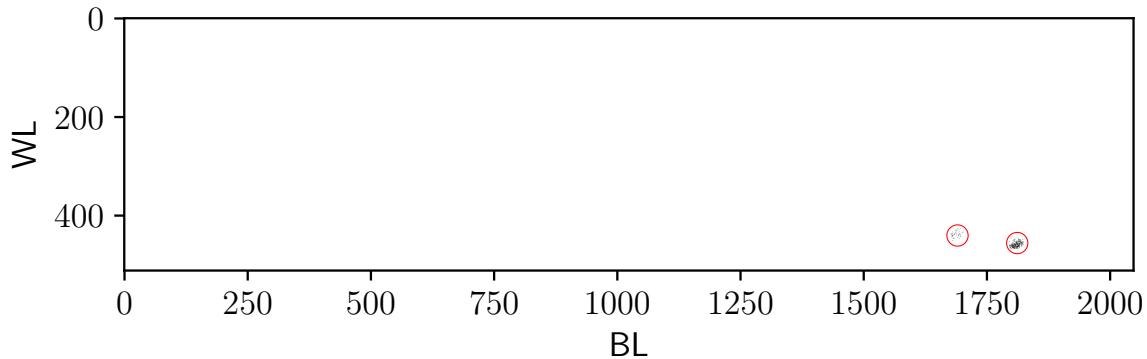

| 5.6  | Cartographie des fautes injectées. $P_{\text{laser}} = 1\,\text{W}$ , $f_{\text{laser}} = 1\,\text{Hz}$ , $T_{\text{pulse}} = 0,9\,\text{s}$                  | 89  |

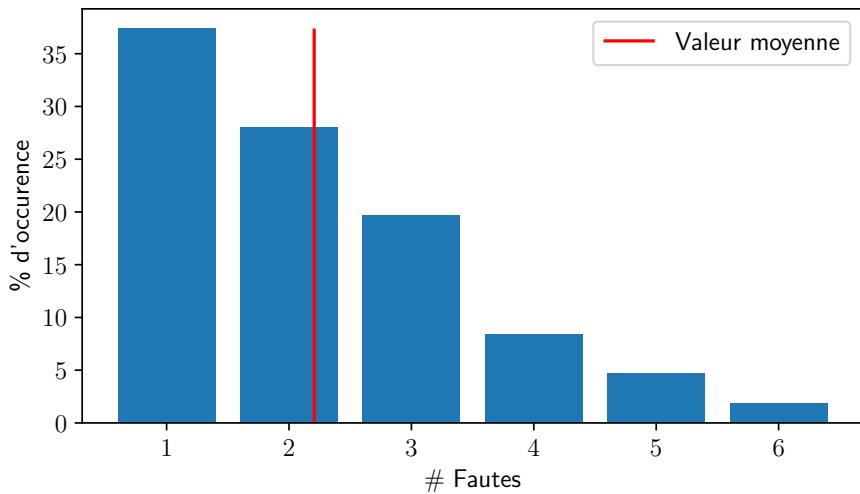

| 5.7  | Distribution expérimentale du nombre de fautes injectées pour l'ensemble des positions. . . . .                                                               | 90  |

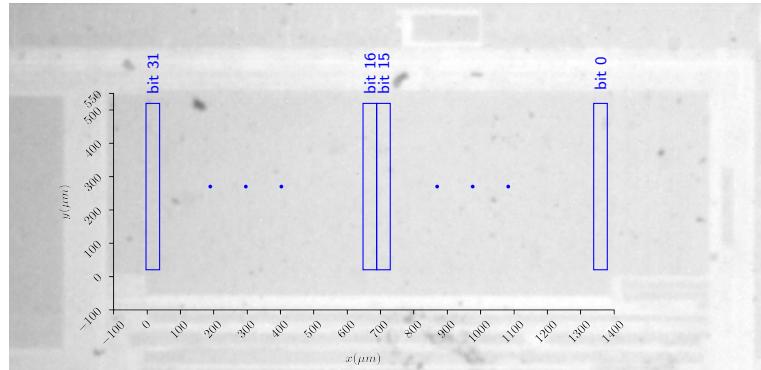

| 5.8  | Ingénierie inverse de l'organisation de la mémoire Flash au niveau bit. . . . .                                                                               | 91  |

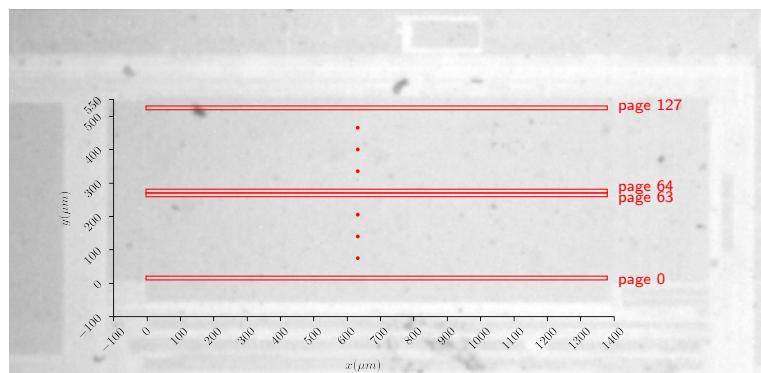

| 5.9  | Ingénierie inverse de l'organisation de la mémoire Flash au niveau page. . . . .                                                                              | 91  |

| 5.10 | Position physique des mots et des bits au sein d'une page de la mémoire. $b_{i,j}$ étant le $i^{\text{ème}}$ bit du $j^{\text{ème}}$ mot de la page. . . . .  | 92  |

| 5.11 | Définition de la S-Box alignée en mémoire dans le code source C. . . . .                                                                                      | 93  |

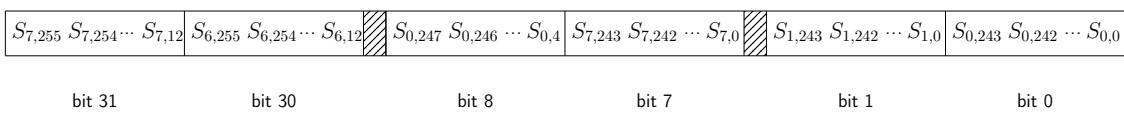

| 5.12 | Implémentation physique de la S-Box en mémoire Flash. $S_{i,j}$ est le $i^{\text{ème}}$ bit du $j^{\text{ème}}$ octet de la S-box. . . . .                    | 93  |

| 5.13 | Organisation sous forme de mots de 32 bits de la S-Box. . . . .                                                                                               | 94  |

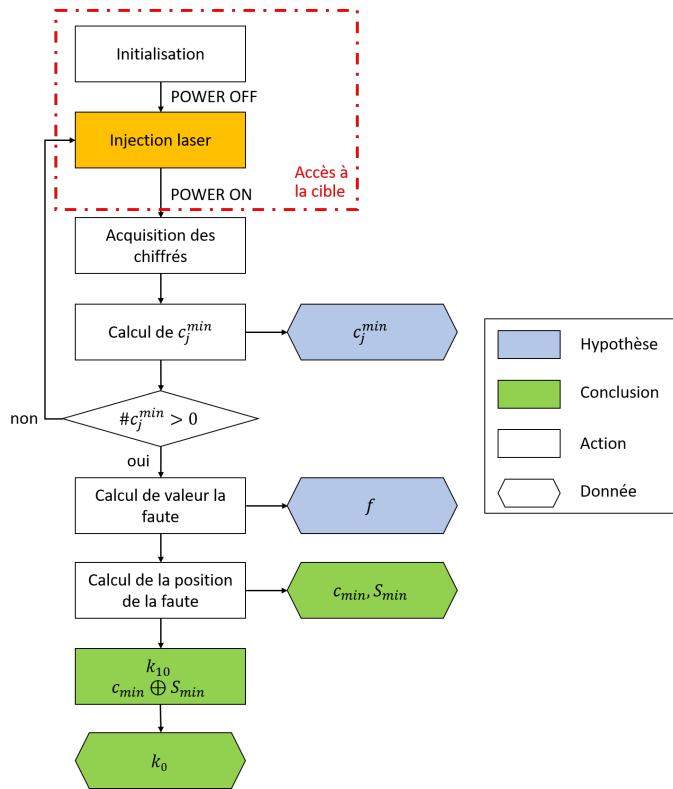

| 5.14 | Protocole expérimental de l'attaque. . . . .                                                                                                                  | 94  |

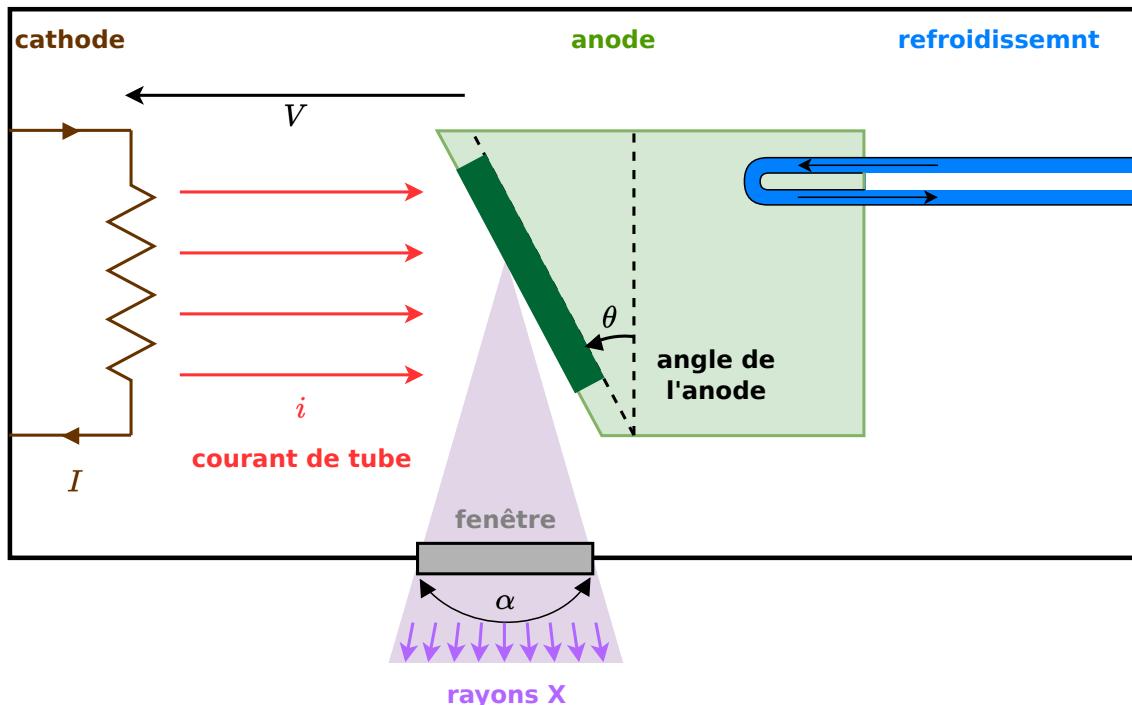

| 6.1  | Illustration de la composition d'un tube X. Adaptée de [Mey23]. . . . .                                                                                       | 103 |

| 6.2  | Irradiateur IDfix. . . . .                                                                                                                                    | 105 |

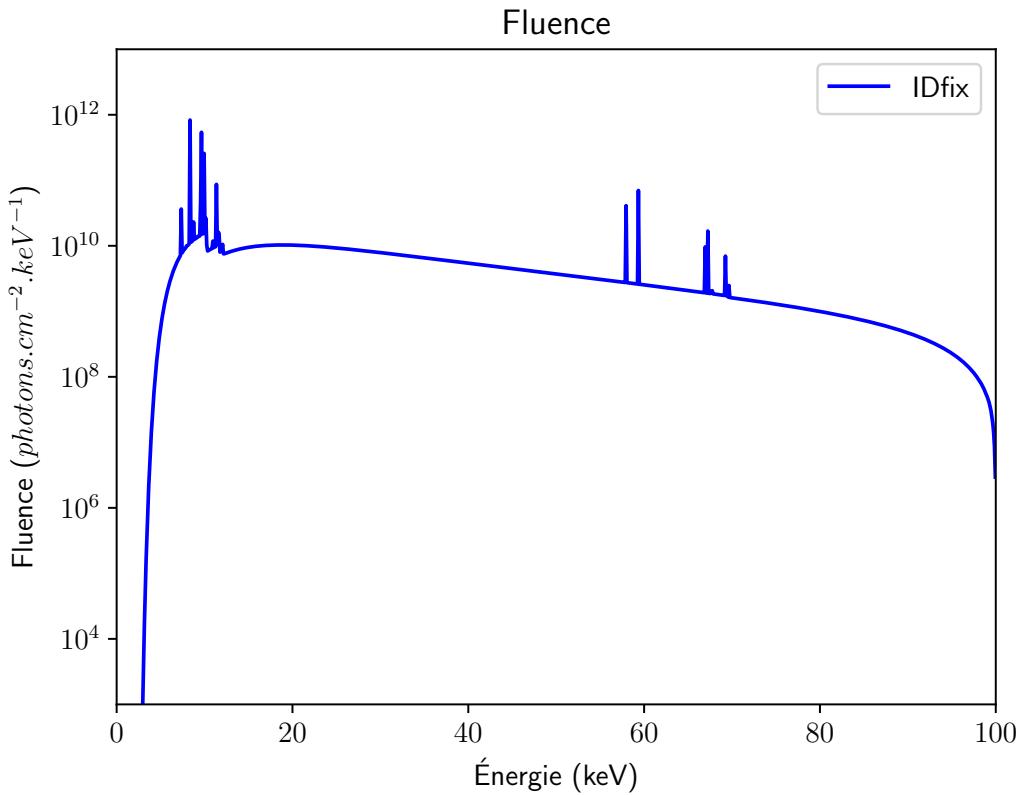

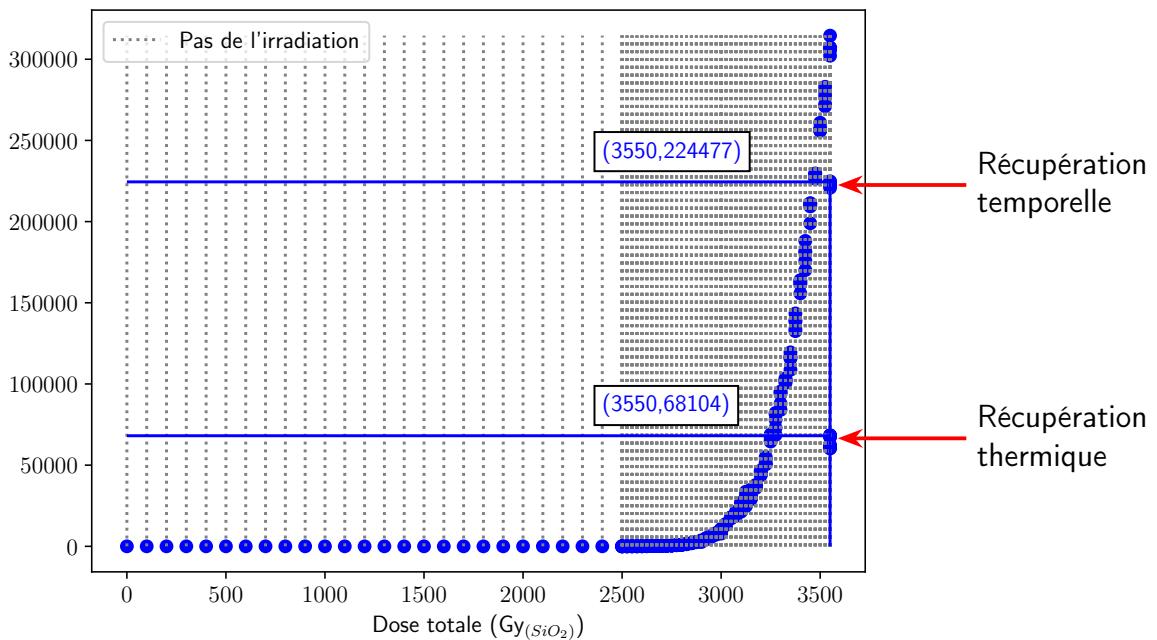

| 6.3  | Spectre simulé de l'irradiateur IDfix obtenu avec une tension de tube de 100 kV, un courant de 45 mA et une distance verticale de 25 cm. . . . .              | 106 |

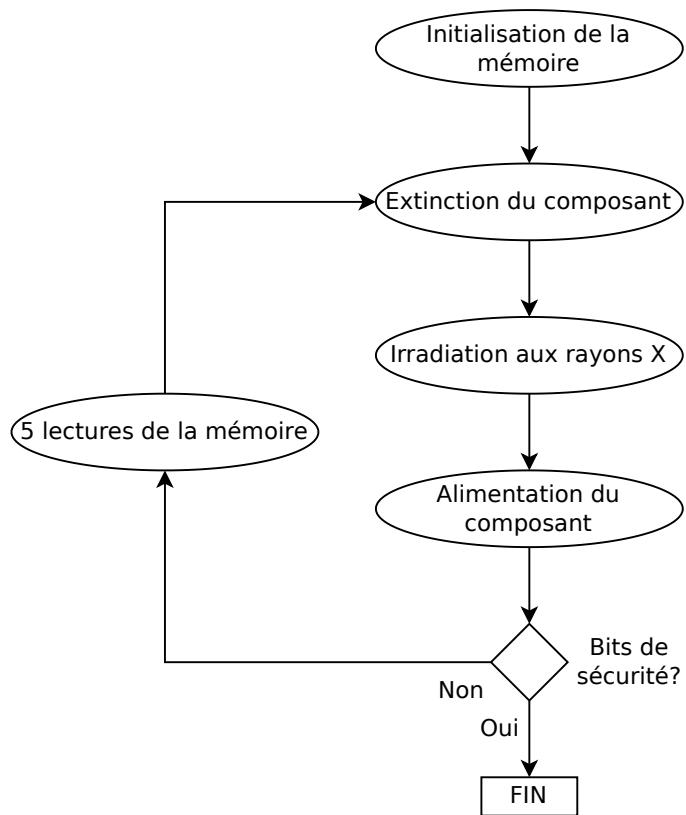

| 6.4  | Protocole expérimental suivi lors des campagnes d'irradiation aux rayons X. . . . .                                                                           | 108 |

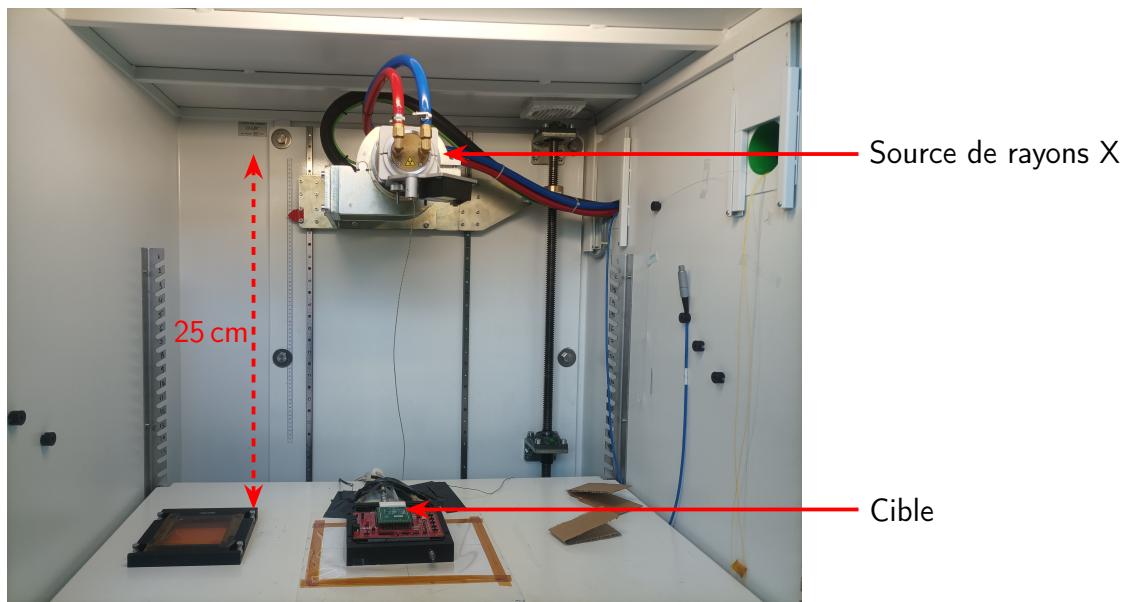

| 6.5  | Photographie de l'intérieur de l'enceinte en plomb avec la source de rayons X et la cible. . . . .                                                            | 108 |

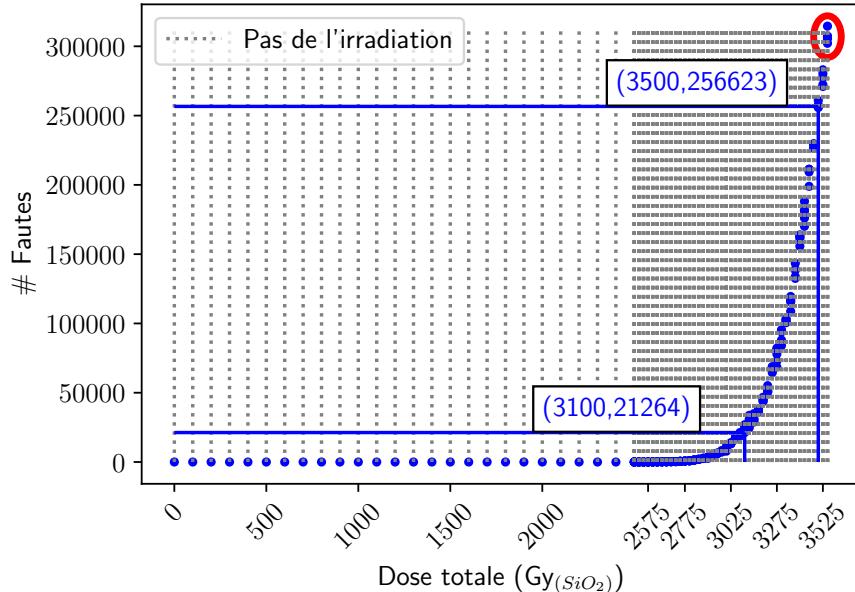

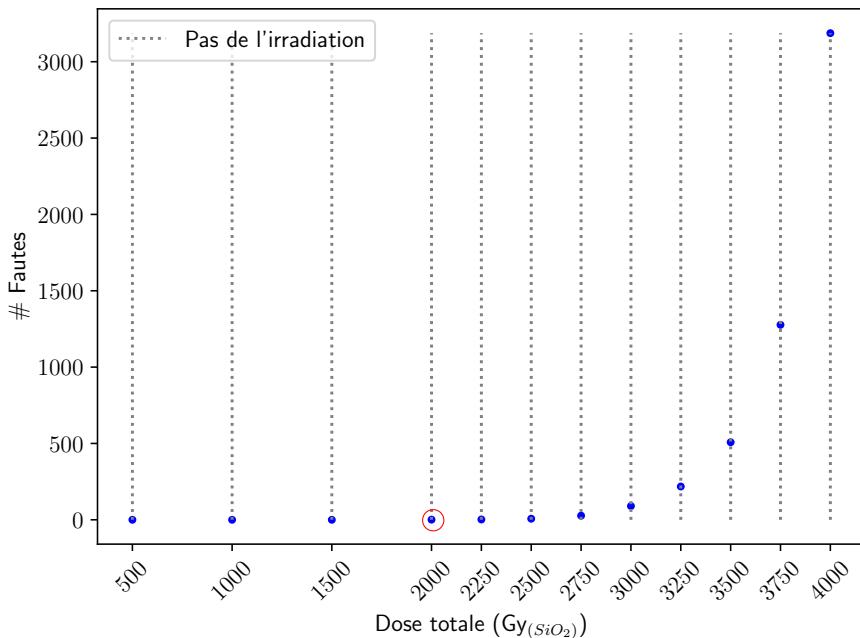

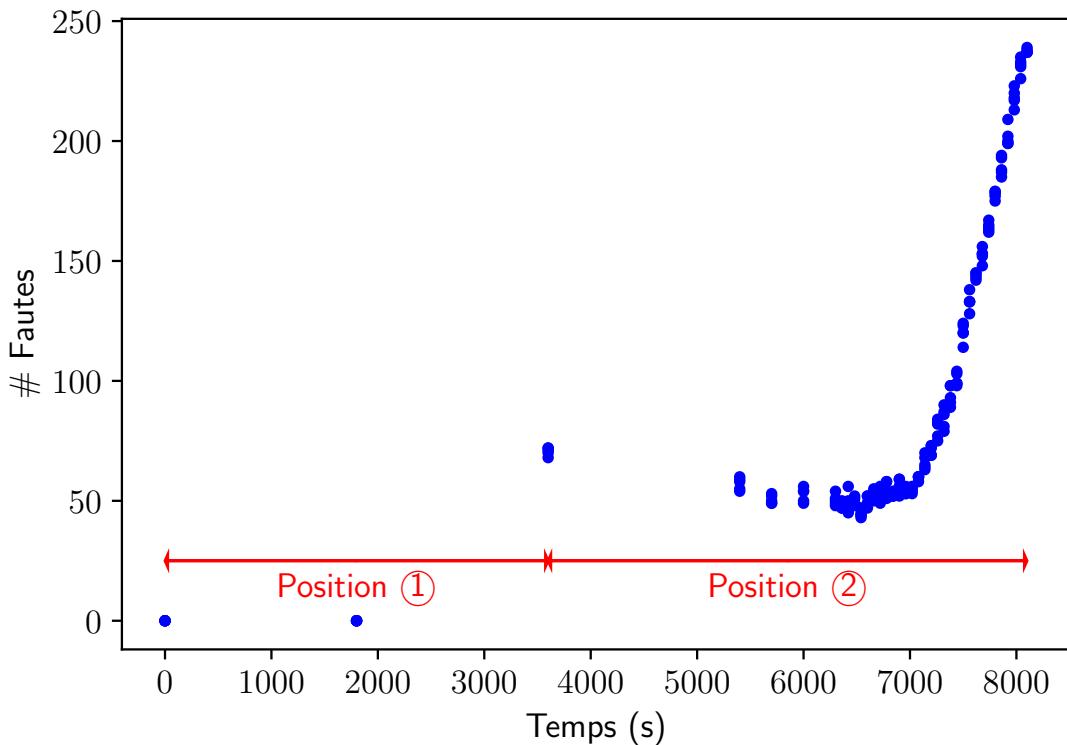

| 6.6  | Évolution du nombre de fautes en mémoire Flash pendant les irradiations aux rayons X. Chaque point bleu correspond à une lecture de la mémoire. 109           | 109 |

|      |                                                                                                                                                                                                   |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

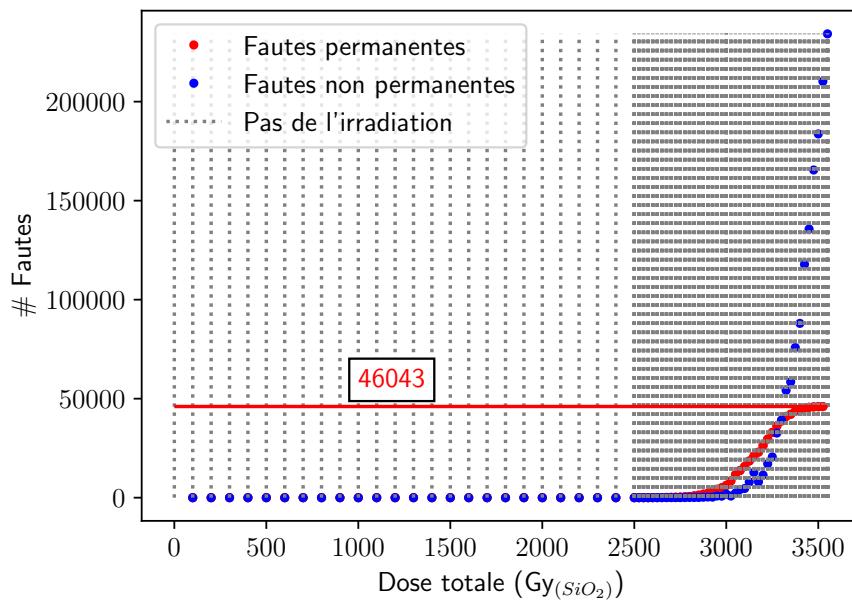

| 6.7  | Évolution du nombre de fautes permanentes en rouge et non permanentes en bleu en mémoire Flash pendant les irradiations aux rayons X . . . . .                                                    | 110 |

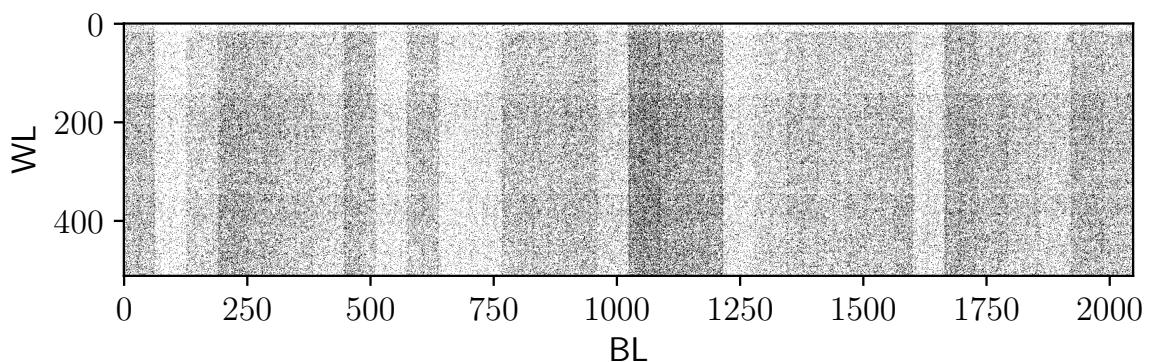

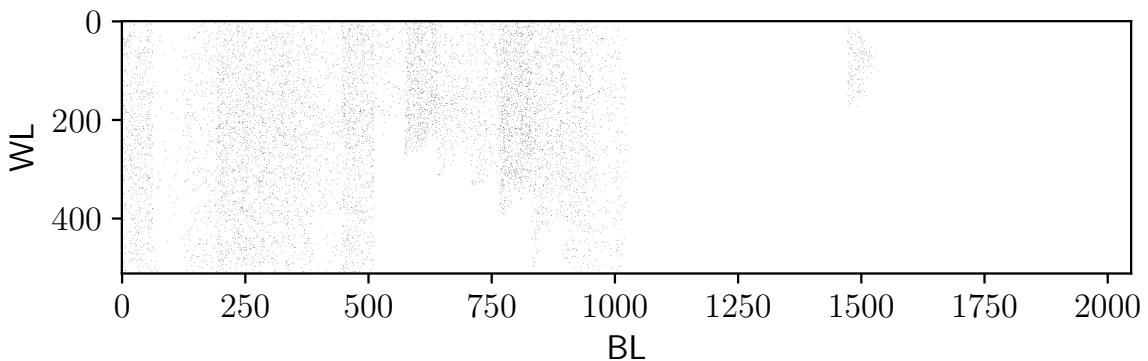

| 6.8  | État de la mémoire Flash à la fin des irradiations aux rayons X. Chaque point représente un bit d'information. . . . .                                                                            | 111 |

| 6.9  | Évolution du nombre de fautes en mémoire EEPROM pendant les irradiations aux rayons X. Chaque point vert correspond à une lecture de la mémoire. . . . .                                          | 112 |

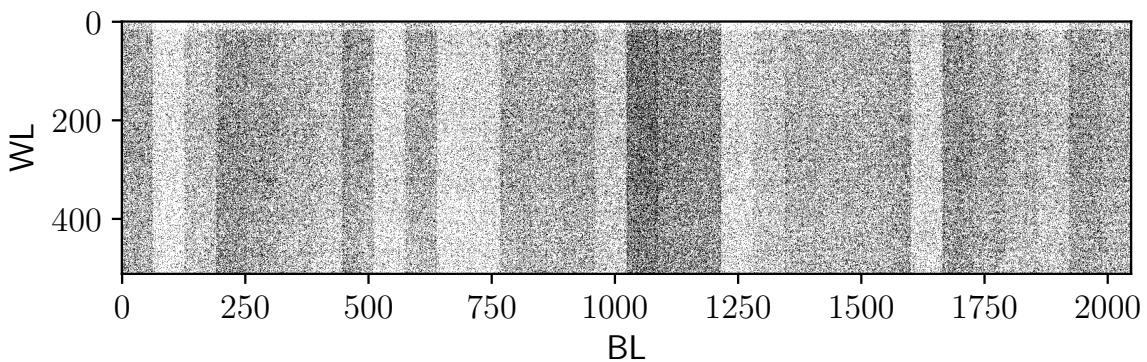

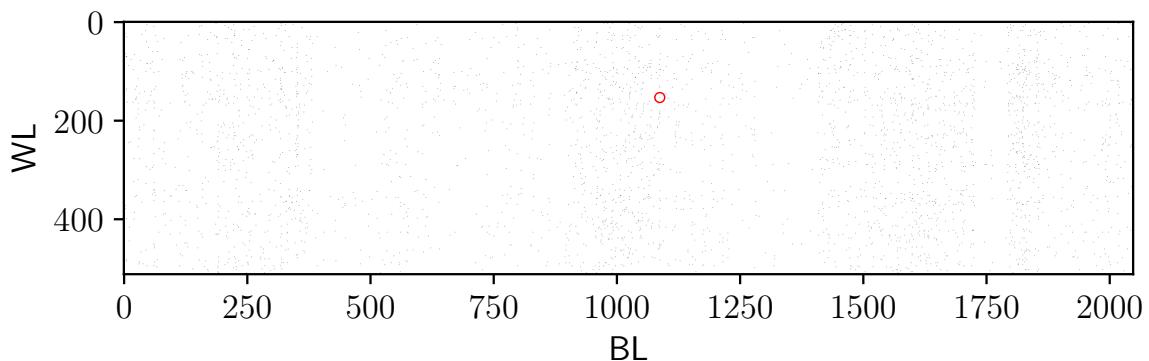

| 6.10 | État de la mémoire Flash après une semaine de récupération à température ambiante. . . . .                                                                                                        | 113 |

| 6.11 | État de la mémoire Flash après récupération temporelle et thermique. . .                                                                                                                          | 113 |

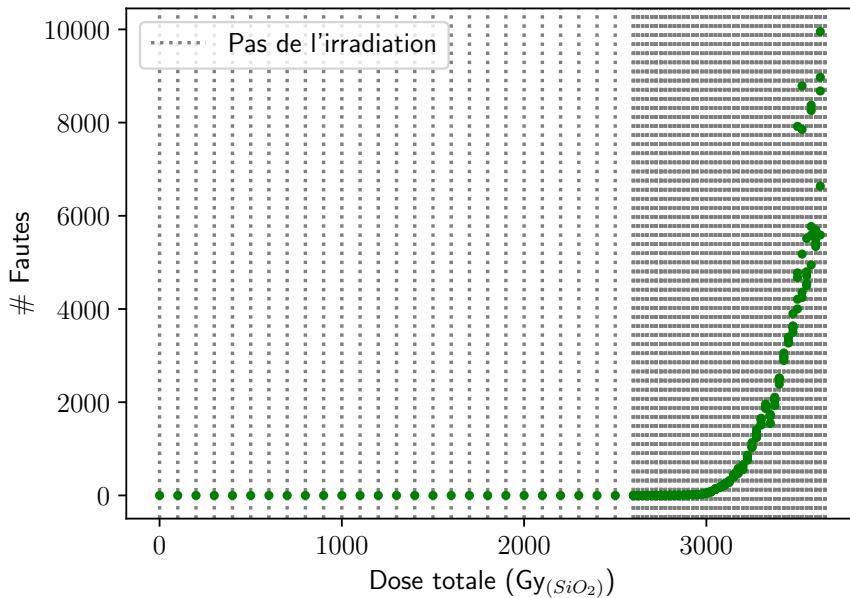

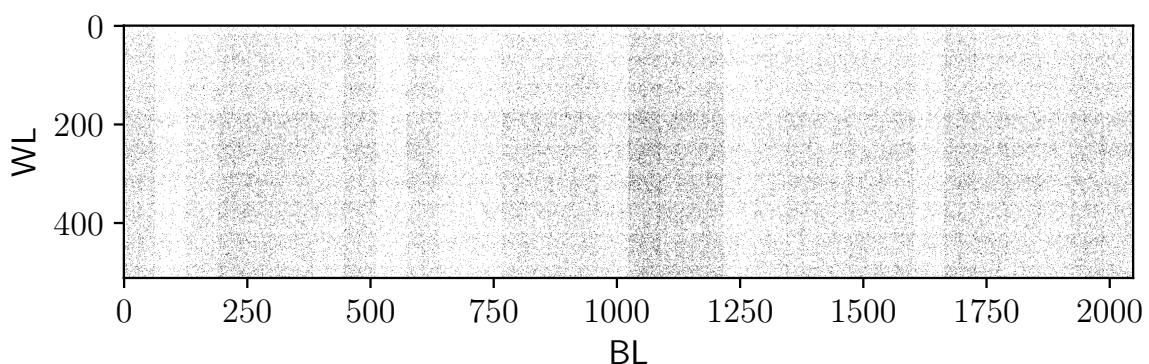

| 6.12 | Évolution du nombre de fautes en mémoire Flash pendant les irradiations aux rayons X avec récupération thermique et temporelle. Chaque point bleu correspond à une lecture de la mémoire. . . . . | 114 |

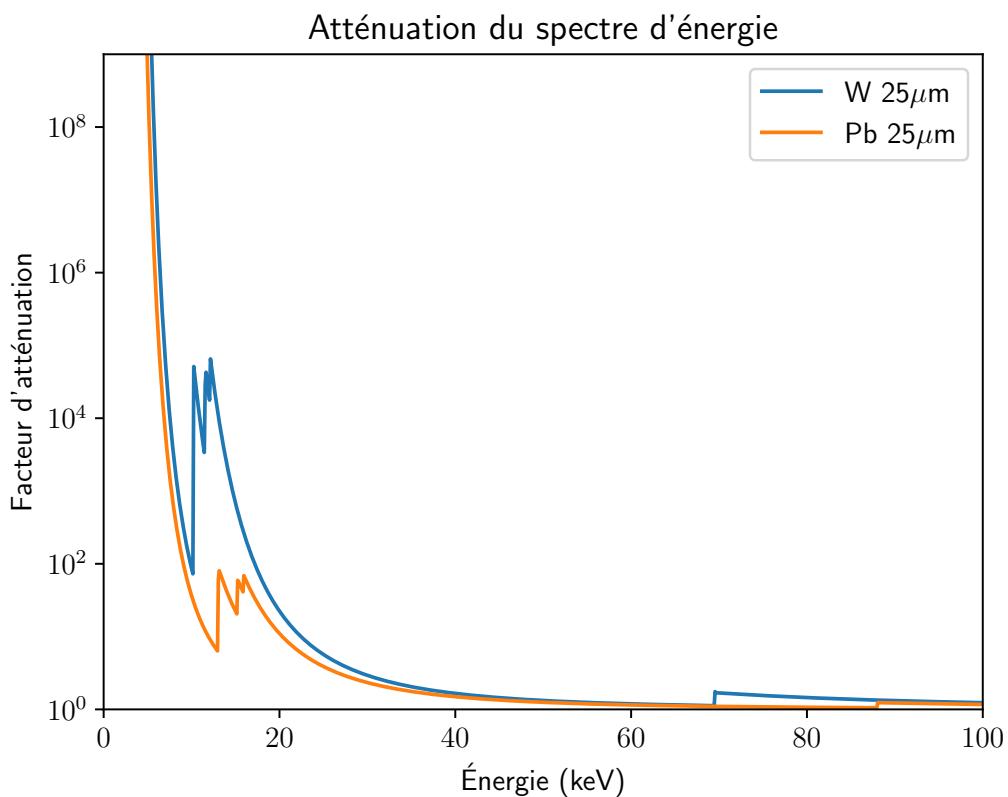

| 6.13 | Simulation du spectre d'énergie avec filtration par un masque en tungstène (W) ou en plomb (Pb) d'épaisseur 25 µm. . . . .                                                                        | 116 |

| 6.14 | Atténuation des masques en plomb et tungstène pour une épaisseur de 25 µm. . . . .                                                                                                                | 117 |

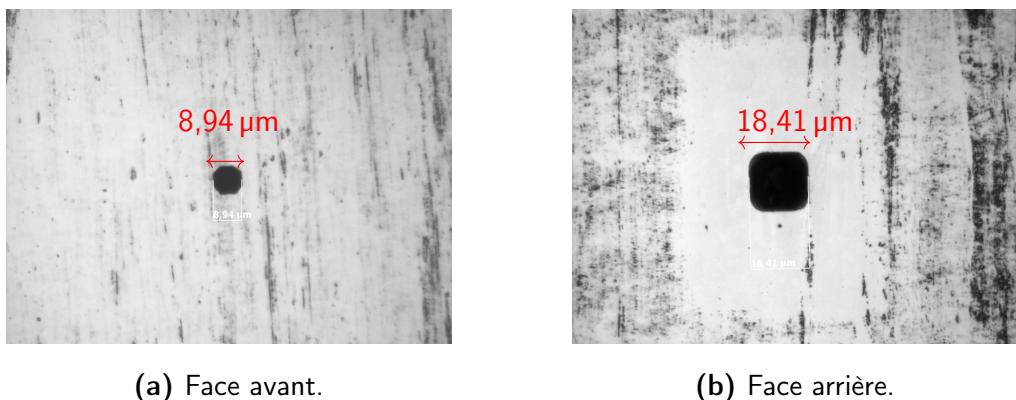

| 6.15 | Images au microscope optique du masque en tungstène. . . . .                                                                                                                                      | 117 |

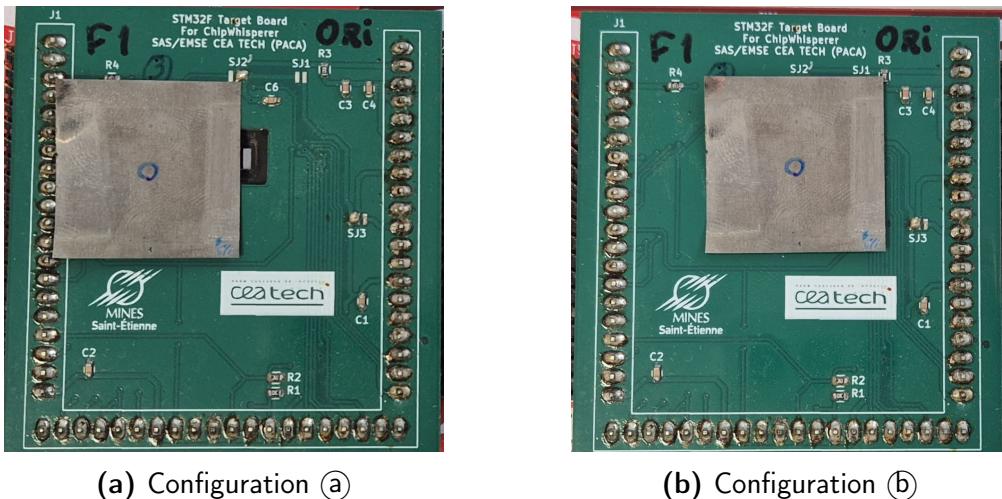

| 6.16 | Positionnements du masque pour les essais d'irradiations aux rayons X. .                                                                                                                          | 118 |

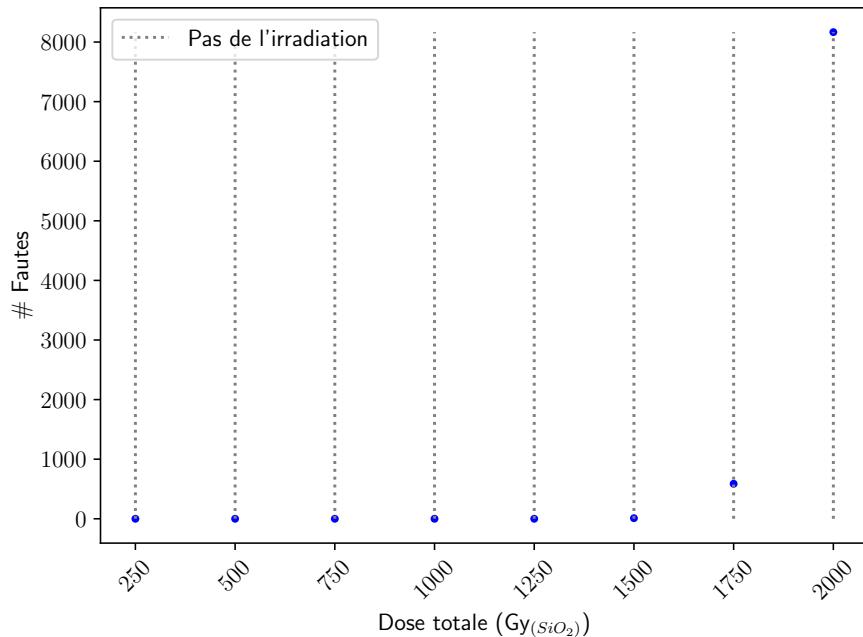

| 6.17 | Évolution du nombre de fautes en mémoires Flash pour la configuration (a). . . . .                                                                                                                | 119 |

| 6.18 | État de la mémoire Flash après les irradiations pour la configuration (a) et une dose totale de 2000 Gy <sub>(SiO<sub>2</sub>)</sub> . . . . .                                                    | 119 |

| 6.19 | Évolution du nombre de fautes en mémoires Flash pour la configuration (b). Entouré en rouge l'apparition d'une faute monobit pour une dose de 2000 Gy <sub>(SiO<sub>2</sub>)</sub> . . . . .      | 120 |

| 6.20 | État de la mémoire Flash après les irradiations pour la configuration (b). Entouré en rouge la première faute monobit apparue pour une dose de 2000 Gy <sub>(SiO<sub>2</sub>)</sub> . . . . .     | 121 |

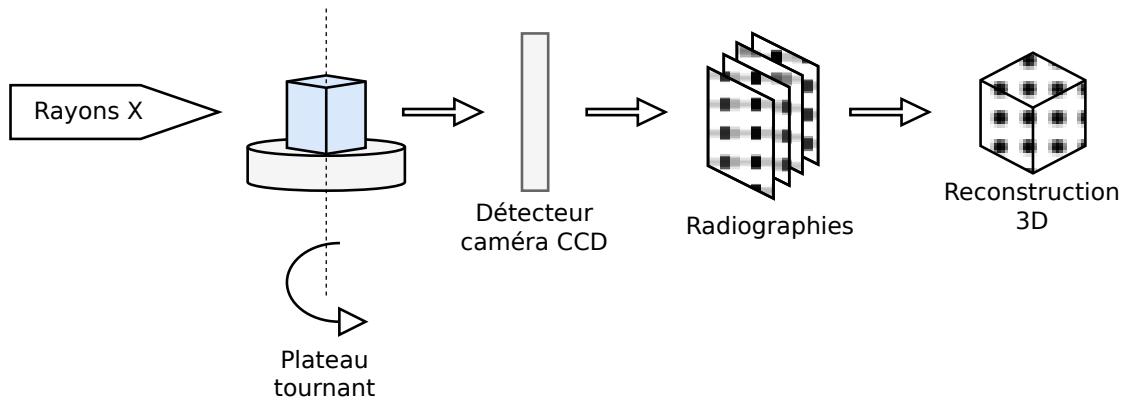

| 6.21 | Description du fonctionnement d'un tomographe. Adapté de [Fal08]. . .                                                                                                                             | 122 |

| 6.22 | Photographie du montage expérimental. . . . .                                                                                                                                                     | 122 |

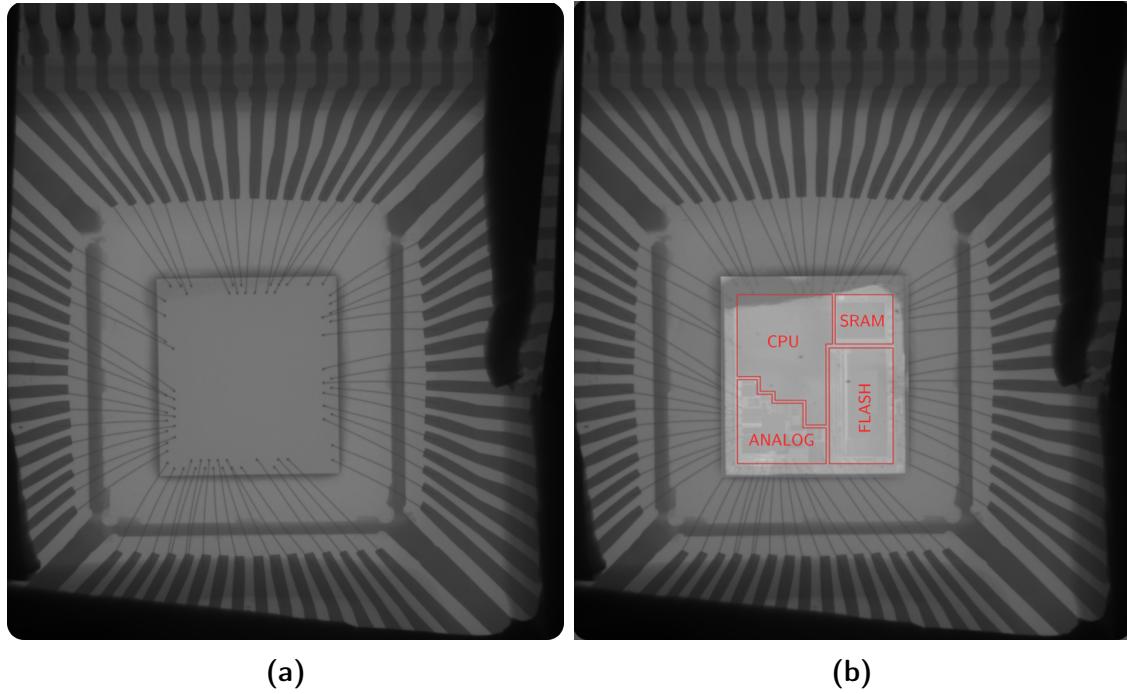

| 6.23 | Images obtenues au tomographe du STM32F100 sans (a) et avec (b) la superposition de l'image IR. . . . .                                                                                           | 123 |

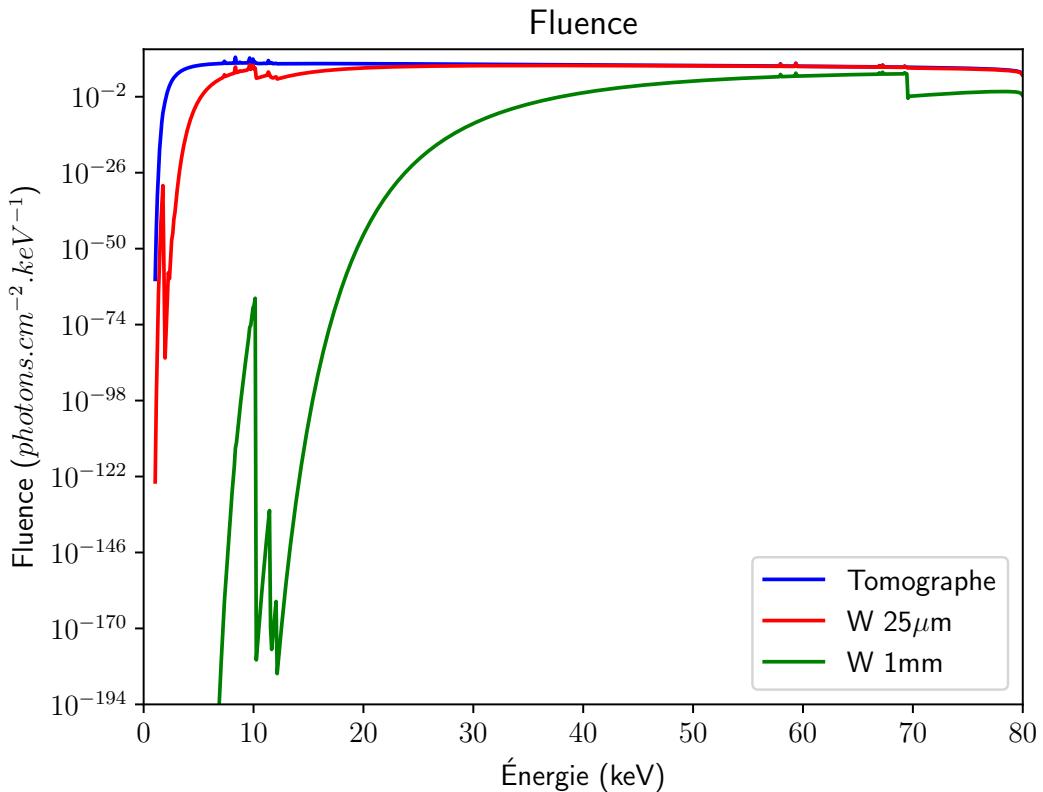

| 6.24 | Spectre simulé du tomographe obtenu avec une tension de tube de 80 kV, un courant de 50 µA et une distance de 5 cm avec ou sans un filtrage par masque (W) d'épaisseur 25 µm ou 1 mm. . . . .     | 124 |

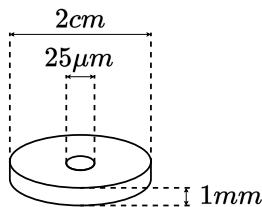

| 6.25 | Schéma du nouveau masque. . . . .                                                                                                                                                                 | 124 |

|                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

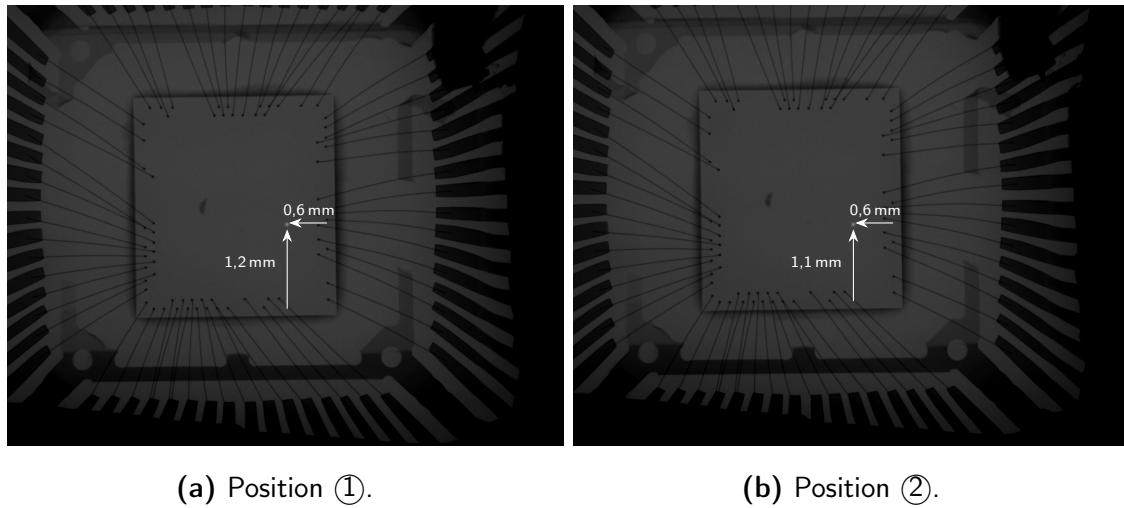

| 6.26 Images obtenues au tomographe de la cible avec le masque pour la configuration ①. . . . .                     | 126 |

| 6.27 Image obtenue au tomographe de la cible avec le masque pour la configuration ② lors de la position ②. . . . . | 127 |

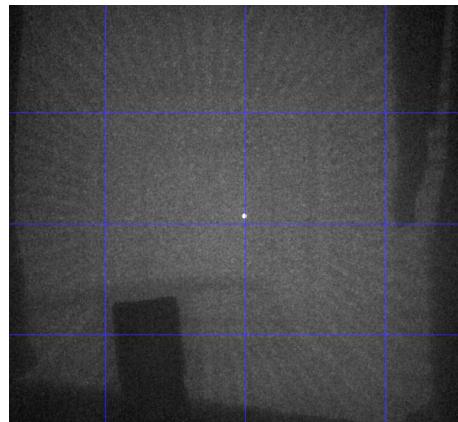

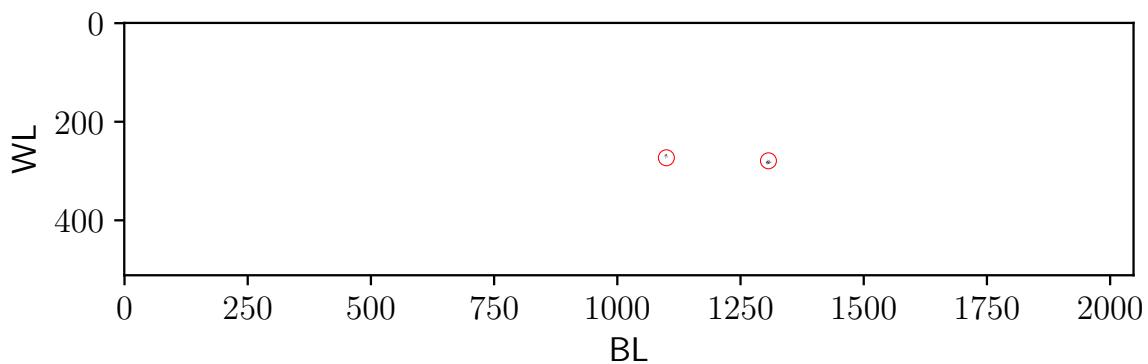

| 6.28 État de la mémoire Flash après 80 min d'exposition à la première position. . . . .                            | 127 |

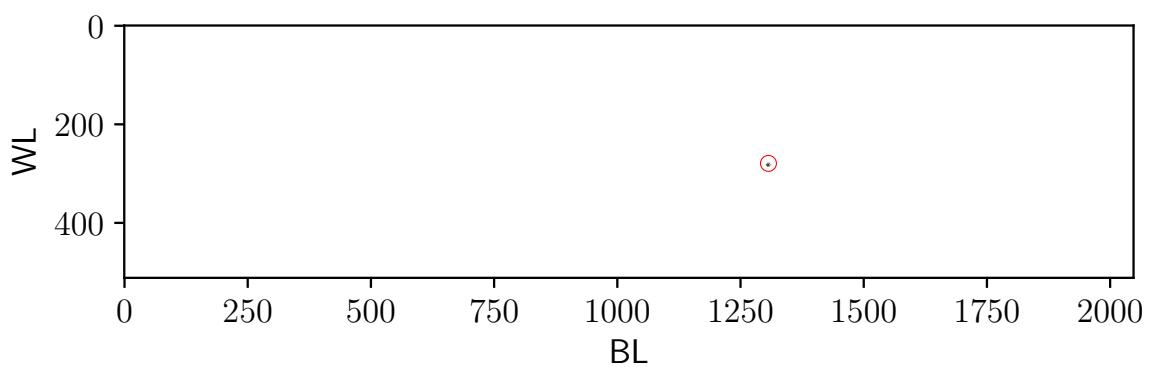

| 6.29 État de la mémoire Flash après 60 min d'exposition à la deuxième position. . . . .                            | 128 |

| 6.30 État de la mémoire Flash après 180 min d'exposition à la troisième position. . . . .                          | 128 |

| 6.31 État de la mémoire Flash après les irradiations des deux positions. . . . .                                   | 129 |

| 6.32 Évolution du nombre de fautes en mémoire Flash avec la configuration ③. . . . .                               | 130 |

# Liste des tableaux

---

|     |                                                                                                                                                                                                                                  |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Différentes versions de l'algorithme AES avec $N_r$ le nombre de rondes. . . . .                                                                                                                                                 | 17  |

| 2.2 | Table de substitution d'AES. . . . .                                                                                                                                                                                             | 19  |

| 2.3 | Nombre moyen de chiffrements nécessaires pour retrouver une information utile à la PFA. . . . .                                                                                                                                  | 25  |

| 3.1 | Définitions de la quantité de particules irradiant un matériau. [Sel+11]. . . . .                                                                                                                                                | 45  |

| 3.2 | Grandeurs usuelles pour quantifier la perte d'énergie linéaire d'une particule chargée. . . . .                                                                                                                                  | 46  |

| 4.1 | Champ visuel et diamètre minimal du spot pour les différents grossissements disponibles. . . . .                                                                                                                                 | 65  |

| 4.2 | Solutions acides utilisées pour la décapsulation. Adapté de [Lim+22]. . . . .                                                                                                                                                    | 66  |

| 4.3 | Encodage des instructions dans le jeu ARM Thumb-2. Les "x" peuvent prendre les valeurs '0' ou '1'. Adapté de [Arm]. . . . .                                                                                                      | 68  |

| 4.4 | Encodage des instructions de traitement de données dans le jeu ARMv7 Thumb. Les "x" peuvent prendre les valeurs '0' ou '1'. Adapté de [Arm]. . . . .                                                                             | 68  |

| 4.5 | Instructions de traitement des données [Arm]. . . . .                                                                                                                                                                            | 69  |

| 4.6 | Encodage des instructions de <i>décalage d'une valeur immédiate</i> , d' <i>addition</i> , de <i>soustraction</i> , de <i>comparaison</i> et de <i>déplacement</i> de données dans le jeu ARMv7 Thumb. Extrait de [Arm]. . . . . | 69  |

| 4.7 | Instructions dites "basiques". [Arm]. . . . .                                                                                                                                                                                    | 69  |

| 4.8 | Nouvelles possibilités de corruption d'opcode pour le jeu d'instruction ARMv7. . . . .                                                                                                                                           | 77  |

| 5.1 | Caractéristiques des objectifs du banc laser Pulscan. . . . .                                                                                                                                                                    | 87  |

| 5.2 | Nombre de candidats restants en fonction du nombre de fautes injectées. . . . .                                                                                                                                                  | 98  |

| 6.1 | Caractéristiques de l'irradiateur IDfix. . . . .                                                                                                                                                                                 | 105 |

| 6.2 | Statut de la protection de la mémoire Flash selon les valeurs de RDP et nRDP. 0xXY représente n'importe quelle valeur différente de 0xFF et 0xA5. [Stm] . . . . .                                                                | 107 |

|     |                                                                                                                               |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Récupération temporelle et thermique. . . . .                                                                                 | 114 |

| 6.4 | Synthèse des atténuations des deux masques obtenues en simulation pour les énergies comprises entre 0 keV et 100 keV. . . . . | 116 |

| 6.5 | Mesure expérimentale de l'efficacité du masque. . . . .                                                                       | 118 |

| 6.6 | Caractéristiques du tomographe. . . . .                                                                                       | 123 |

# Liste des sigles

---

- AES** Advanced Encryption Standard. [vii](#), [3–5](#), [8](#), [16](#), [17](#), [23](#), [40](#), [92](#), [93](#), [95](#), [98](#), [100](#), [134](#)

- AMFoRS** Architectures and Methods for Resilient Systems. [6](#)

- ANR** Agence Nationale de la Recherche. [5](#)

- BBRAM** Battery Backed RAM. [34](#)

- BGA** Ball Grid Array. [44](#)

- BTI** Bias Temperature Instability. [54](#), [56](#)

- CARDIS** Smart Card Research and Advanced Application Conference. [60](#)

- CC** Critères Communs. [65](#)

- CEA** Commissariat à l'Énergie Atomique et aux énergies alternatives. [5](#)

- CFI** Control Flow Integrity. [4](#), [27](#)

- CME** Coronal Mass Ejection. [41](#), [43](#)

- CMOS** Complementary Metal-Oxide-Semiconductors. [xiii](#), [xiv](#), [8](#), [32](#), [35](#), [36](#), [53](#), [54](#), [67](#)

- CNRS** Centre National de la Recherche Scientifique. [5](#)

- CTSYS** Sûreté et Sécurité des Systèmes embarqués et distribués. [6](#)

- DDD** Displacement Damage Dose. [48](#)

- DES** Data Encryption Standard. [16](#), [23](#)

- DFA** Differential Fault Analysis. [23](#), [121](#)

- DMD** Digital Micromirror Device. [61](#)

- DOE** Diffractive Optical Element. [61](#)

- DPA** Differential Power Analysis. [2](#)

- DRAM** Dynamic Random Access Memory. [53](#)

- ECC** Error Correcting Code. [27](#)

- EDAC** Error Detection and Correction. [4](#)

- EEPROM** Electrically Erasable Programmable Read-Only Memory. [xvi](#), [4](#), [10](#), [11](#), [15](#), [51](#), [112](#)

- EMI** Injection électromagnétique. [27](#)

- EMP** Impulsion électromagnétique. [27](#)

- EPROM** Erasable Programmable Read-Only Memory. [10](#), [11](#)

- FIB** Focused Ion Beam. [3](#), [4](#), [116](#)

- FPGA** Field Programmable Gate Arrays. [23](#), [34](#), [134](#), [135](#)

- FSA** Fault Sensitivity Analysis. [36](#), [37](#)

- FWHM** Full-Width at Half Maximum. [61](#), [82](#), [83](#), [87](#)

- GCR** Galactic Cosmic Rays. [41](#), [42](#)

- HCI** Hot Carrier Injection. [56](#)

- IoT** Internet of Things. [vii](#), [viii](#), [1](#), [65](#), [85](#), [93](#), [99](#), [133](#), [134](#)

- ISA** Instruction Set Architecture. [22](#)

- LabHC** Laboratoire Hubert Curien. [5](#), [129](#)

- LCIS** Laboratoire de Conception et d'Intégration des Systèmes. [6](#)

- LET** Linear Energy Transfer. [46](#)

- MCU** MicroController Unit. [37](#)

- MLE** Maximum Likelihood Estimation. [24](#)

- MOPERE** Materials for Optics and Photonics in Extreme Radiation Environments. [104](#)

- MOS** Metal Oxide Semiconductor. [8](#), [11](#), [54](#), [111](#), [114](#), [130](#), [134](#)

- MOSFET** Metal-Oxide-Semiconductor Field-Effect Transistor. [8](#)

- MSE** Mines de Saint-Étienne. [5](#), [6](#)

- NBTI** Negative-BTI. [xiv](#), [54](#), [55](#)

- NIST** National Institute of Standards and Technology. [16](#)

- NMOS** Negative MOS. [xiii](#), [xiv](#), [8](#), [9](#), [34–36](#), [49](#), [50](#)

- PAIN** Physical Assurance and Inspection of Electronics. [102](#)

- PBTI** Positive-BTI. [54](#)

- PCB** Printed Circuit Board. [44](#)

- PFA** Persistent Fault Analysis. [5](#), [23–25](#), [85](#), [90](#), [92](#), [94–96](#), [98–100](#), [133](#), [135](#)

- PMOS** Positive MOS. [xiii](#), [8](#), [9](#), [35](#), [36](#), [49](#)

- POP** Power-Off laser attacks on security Primitives. [5](#)

- PUF** Physically Unclonable Functions. [135](#)

- RSA** Rivest-Shamir-Adleman. [22](#)

- SAA** South Atlantic Anomaly. [43](#)

- SAS** Systèmes et Architectures Sécurisés. [5](#)

- SEE** Single Event Effect. [20, 48, 52](#)

- SEFI** Single Event Functional Interrupt. [20, 53](#)

- SEL** Single Event Latch-up. [53](#)

- SESAM** Systèmes Embarqués Sécurisés et Architectures Matérielles. [5](#)

- SET** Single Event Transient. [20, 36, 52, 53](#)

- SEU** Single Event Upset. [20, 36, 53](#)

- SFA** Statistical Fault Analysis. [23](#)

- SIFA** Statistical Ineffective Fault Attack. [23](#)

- SIMaP** Science et Ingénierie des Matériaux et des Procédés. [115, 121](#)

- SLM** Spatial Light Modulator. [61](#)

- SoC** System On Chip. [134](#)

- SOI** Silicon On Insulator. [53](#)

- SPA** Simple Power Analysis. [2](#)

- SRAM** Static Random Access Memory. [xiii, 9, 10, 36, 37, 49](#)

- TCRES** Transactions on Cryptographic Hardware and Embedded Systems. [80](#)

- TDDB** Time-Dependant-Dielectric Breakdown. [xiv, 56, 57](#)

- TID** Total Ionizing Dose. [xiv, 48–51](#)

- TIMA** Techniques of Informatics and Microelectronics for integrated systems Architecture. [6](#)

- TRNG** True Random Number Generator. [135](#)

- UGA** Université Grenoble-Alpes. [6, 121](#)

- UJM** Université Jean-Monnet de Saint-Étienne. [5](#)

- ZCE** Zone de charge d'espace. [32](#)

# Chapitre 1

## Introduction générale

### 1.1 Positionnement du problème

Les progrès réalisés dans le domaine de la microélectronique ces dernières décennies ont permis la démocratisation des circuits intégrés. Ces progrès permettent la fabrication à bas coût, une forte augmentation de la puissance de calcul et une nette diminution de la consommation énergétique des composants. De nombreuses applications, notamment dans le cadre de l'*Internet of Things* (IoT), sont devenues possibles grâce à l'existence de ces nouveaux circuits intégrés communicants. Aujourd'hui, les objets connectés à base de ces circuits intégrés sont omniprésents dans de nombreux secteurs tels que celui de la domotique, des télécommunications, ou encore les secteurs bancaire, médical ou militaire.

Avec la démocratisation de ces objets connectés s'est posée la question de leur sécurité. En effet, les objets connectés peuvent contenir des informations sensibles concernant des biens, des infrastructures ou encore des personnes. La sécurité des données stockées et/ou manipulées est assurée mathématiquement par l'implémentation de primitives de sécurité comme les algorithmes cryptographiques. Ceux-ci doivent garantir notamment trois propriétés : l'*intégrité*, la *confidentialité* et l'*authenticité*. L'intégrité désigne la non-altération malicieuse d'une donnée après sa création, la confidentialité assure qu'unique-ment les parties dans le secret ont accès à l'information et l'authenticité que l'origine de la donnée est certifiée et identifiée.

En revanche, l'implémentation matérielle de ces primitives peut contenir des failles exploitable par un attaquant. Ces failles ne sont pas nécessairement dues à une implémentation incorrecte des algorithmes, mais à des propriétés intrinsèques liées à la fabrication ou à la technologie des composants. Lorsqu'un circuit est en fonctionnement, des informations directement liées à son activité peuvent être extraites par le biais de diverses grandeurs physiques mesurables comme ses émanations électromagnétiques ou sa consommation

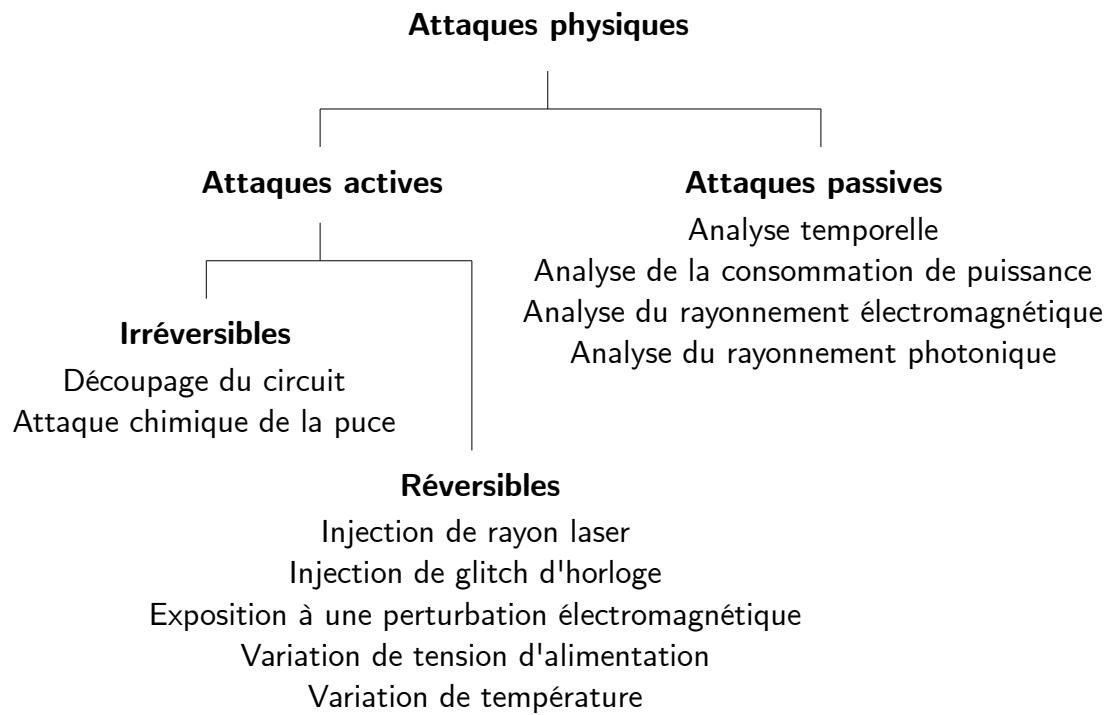

Figure 1.1 – Classification des attaques physiques [Bos18].

de puissance. Symétriquement, le fonctionnement d'un circuit peut être perturbé par des facteurs extérieurs comme une tension d'alimentation du circuit ou une température en dehors de leurs plages nominales ou des particules qui peuvent être radiatives.

Les phénomènes décrits précédemment peuvent être exploités par un adversaire pour attaquer physiquement un système cryptographique. On peut distinguer différents types d'attaques physiques. D'une part, les attaques passives sont basées sur la mesure de grandeurs physiques émanant du circuit pour retrouver de l'information sensible sur le système. D'autre part, les attaques actives visent à obtenir un fonctionnement détourné du circuit qui permet de retrouver de l'information secrète. Dans les deux cas, un attaquant cherche à induire ou à exploiter une fuite d'information. La Figure 1.1 classifie ces différents types d'attaques.

Les attaques passives sont souvent plus simples à mettre en place. Parmi ces dernières, on peut citer l'analyse temporelle (étude du temps d'exécution d'un programme ciblé), de la consommation de puissance, du rayonnement électromagnétique ou photonique. La corrélation entre les données secrètes manipulées par le circuit et la présence d'information contenue dans les canaux auxiliaires a été démontré par Kocher en 1996 [Koc96]. Il existe plusieurs schémas permettant d'extraire une clé de chiffrement d'un algorithme cryptographique tels que l'analyse simple de consommation (SPA pour *Simple Power Analysis*) ou l'analyse différentielle de la consommation (ou DPA pour *Differential Power Analysis*)

Analysis) [Koc96 ; KJJ99]. Une très faible quantité d'informations qui fuite du système peut être exploitée pour attaquer un algorithme de cryptographie mathématiquement très robuste.

Les attaques actives quant à elles peuvent encore être scindées en deux sous-catégories : les attaques irréversibles et les attaques réversibles. Dans le cas des attaques irréversibles le système attaqué est altéré de façon permanente, voire détruit. On peut citer l'abrasion chimique, la découpe laser ou l'édition avec un faisceau d'ions focalisés (FIB pour *Focused Ion Beam*) du circuit. Il est également possible de sonder les signaux internes d'un circuit altéré au FIB pour extraire des informations [Gou+23]. Ces attaques sont principalement utilisées dans le but d'effectuer de l'ingénierie inverse, c'est-à-dire d'obtenir des informations sur la conception et l'architecture du circuit ou pour permettre d'autres attaques. Par exemple, une attaque par sondage grâce à un FIB est alors une attaque par observation (passive). Les attaques réversibles nécessitent une préparation de l'échantillon, comme l'ouverture du boîtier par exemple, qui n'est pas nécessairement destructive. On y trouve classiquement les injections laser [Col+19 ; Men+20b ; Lim+22] ou électromagnétique [Men+19 ; Men+20a], les *glitches* d'horloge [BGV11] ou de tension d'alimentation [Zus+14] ou encore les variations de température [Sko09]. Elles sont souvent regroupées sous l'appellation d'attaques en fautes. Les attaques actives (réversibles ou non) nécessitent un temps, des moyens, des connaissances techniques et des informations sur le système, cela rend ces attaques plus complexes à mettre en œuvre.

Les attaques par injections de fautes peuvent aussi être classées en deux catégories : les attaques globales et locales. Les attaques globales perturbent le fonctionnement de l'entièreté du composant. C'est le cas des *glitches* de tension d'alimentation [Zus+14 ; O'F16 ; BFP19] et d'horloge [Ago+10c ; BGV11]. Les attaques locales visent à modifier le comportement du système en altérant une des parties spécifiques du composant. C'est notamment le cas pour l'injection de fautes par exposition à une impulsion laser ou à une perturbation électromagnétique.

La majorité des études publiées sur les attaques par injection de fautes laser ont été menées à l'aide d'un banc laser monospot, c'est-à-dire ne comportant qu'une seule source laser [Ago+10a ; Ago+10b ; Dut+18 ; Col+19 ; Dut+19 ; Men+20b]. Ces attaques ont permis de mettre en défaut des algorithmes de chiffrement comme AES. Les bancs laser utilisés dans ces travaux possèdent les mêmes limitations. En effet, les temps de déplacement mécanique du spot laser empêchent un attaquant de cibler des positions différentes à des instants proches ou de fauter deux positions différentes en même temps. Cette limitation a été partiellement levée avec l'apparition des bancs laser bispot [Dum+21 ; VDL22 ; Vie+24]. Cette évolution des bancs laser a permis d'envisager des scénarios d'attaques plus évolués.

À quelques exceptions près, la majeure partie des travaux existants dans le domaine de l'injection de fautes ont été réalisés sur des circuits en fonctionnement et donc alimentés en énergie. Dans ce cas, des capteurs sont capables de détecter l'injection de fautes et permettent aux circuits de réagir en conséquence. Par exemple, en 2006, Neto *et al.* ont proposé un capteur permettant de détecter des courants transitoires anormaux dans le substrat pendant un tir laser [Net+06]. D'autre part, dans [Ber+14], une solution utilisant des capteurs numériques et analogiques, tirant ainsi parti des avantages de chaque méthode, est proposée pour détecter les *glitches* de tensions. Pour finir, en 2016 El-Baze *et al.* [ERM16] ont décrit une solution entièrement numérique qui permet la détection d'injection d'ondes électromagnétiques basée sur l'étude des violations des temps de propagation. Il existe aussi d'autres méthodes qui ne sont pas basées sur l'utilisation de capteurs. On peut citer les mécanismes de *Control Flow Integrity* (CFI) qui détectent des comportements anormaux dans l'exécution d'un programme, ou les principes de redondances et les codes détecteurs et correcteurs d'erreurs (*Error Detection and Correction* (EDAC)) qui peuvent également détecter de mauvaises exécutions du code ou des erreurs dans ce dernier. Bien qu'efficaces, ces contre-mesures sont dites *actives* car elles ne fonctionnent que sur des composants alimentés en énergie. En revanche, lors de l'exécution d'un code source corrompu, c'est-à-dire lorsque le résultat d'une injection de faute au sein de la mémoire Flash d'un circuit non alimenté sera exploité, ces contremesures conservent leur efficacité.

En 2009, Schmidt *et al.* [SHP09] ont réussi à retrouver une clé AES en modifiant la boîte de substitution (S-Box) stockée en mémoire EEPROM d'un composant non alimenté par une exposition prolongée à une lumière UV. La méthode proposée repose sur une analyse différentielle qui nécessite d'avoir des chiffrés corrects et des chiffrés fautés. La cryptanalyse développée dans ces travaux n'exploite pas la persistance des fautes. D'autres travaux basés sur la modification physique d'un circuit non alimenté à l'aide d'un FIB (*Focused Ion Beam*) ont permis la désactivation de fonctions de sécurité et de contremesures. Cette méthode possède l'inconvénient d'être irréversible, très coûteuse et complexe à mettre en place.

Force est de constater que malgré les nombreuses études sur les attaques par injections de fautes, il en existe très peu qui abordent les injections multiples de fautes [Vie+23] et les attaques de circuits éteints [Sko09].

## 1.2 Plan et contributions

L'objectif de ces travaux est donc d'évaluer les possibilités d'attaques par injection de fautes plus évoluées qui aillent au-delà de l'état de l'art. L'utilisation d'un banc laser

multispot sur des circuits alimentés, ainsi que des attaques par injection de fautes laser ou rayons X sur circuits non alimentés peuvent prendre en défaut les contremesures existantes. Ces études seront détaillées dans ce manuscrit.

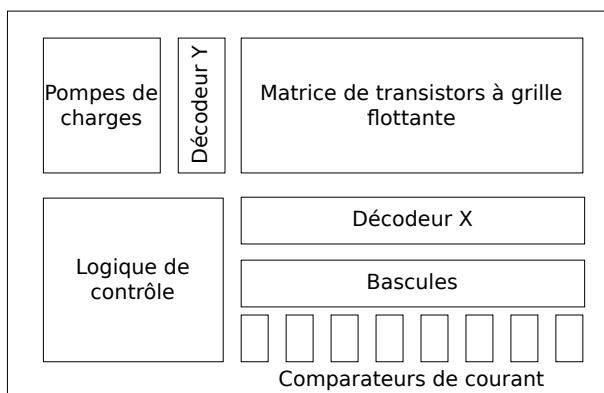

Le [Chapitre 2](#) décrit quelques notions préliminaires nécessaires à la compréhension des travaux décrits dans ce manuscrit. La structure et le fonctionnement de la technologie MOS, des mémoires volatiles et non volatiles sont abordés dans ce chapitre. L'algorithme de chiffrement symétrique AES est également décrit dans ce chapitre. Pour finir, une revue des différents types d'attaques en fautes et de leur exploitation est réalisée.

Le [Chapitre 3](#) synthétise l'état de l'art des effets du laser et des radiations sur les circuits électroniques. Les effets du vieillissement sont aussi décrits dans ce chapitre.

Le [Chapitre 4](#) décrit l'utilisation d'un banc laser multispot. Les avantages, spatiaux et temporels, qui permettent de s'affranchir des limites d'un banc laser monospot sont démontrés dans ce chapitre [[Col+22](#)]. Les nouvelles possibilités d'attaques offertes par ce nouveau banc laser sont également explorées.

Le [Chapitre 5](#) démontre la possibilité d'injecter des fautes permanentes au sein d'une mémoire Flash non alimentée en utilisant une source laser classiquement utilisée en injection laser. Une caractérisation des fautes obtenues du niveau physique au niveau logique est réalisée. Les résultats obtenus sont appliqués dans le cadre de l'Analyse de Faute Persistante (PFA pour *Persistent Fault Analysis*) [[Gra+24](#)].

Le [Chapitre 6](#) analyse l'utilisation d'une source diffuse de rayons X pour corrompre le contenu de mémoires Flash d'un circuit non alimenté [[GBD23](#)]. La réalisation et l'exploitation d'un masque permettant de focaliser les injections de fautes sont également abordées.

## 1.3 Contexte

Cette thèse est réalisée dans le cadre du projet Power-Off laser attacks on security Primitives (POP) ou *Attaques laser de primitives de sécurité non alimentées* financé par l'Agence Nationale de la Recherche (ANR) et est réalisé en collaboration avec quatre équipes de recherche :

- Systèmes Embarqués Sécurisés et Architectures Matérielles (SESAM) du Laboratoire Hubert Curien (LabHC) de l'Université Jean-Monnet de Saint-Étienne (UJM) et le Centre National de la Recherche Scientifique (CNRS)

- Systèmes et Architectures Sécurisés (SAS) de Mines de Saint-Étienne (MSE) et du Commissariat à l'Énergie Atomique et aux énergies alternatives (CEA)

- Sûreté et Sécurité des Systèmes embarqués et distribués (CTSYS) du Laboratoire de Conception et d'Intégration des Systèmes (LCIS) de l'Université Grenoble-Alpes (UGA)

- Architectures and Methods for Resilient Systems (AMFoRS) du laboratoire Techniques of Informatics and Microelectronics for integrated systems Architecture (TIMA) de l'Université Grenoble-Alpes (UGA)

Cette thèse s'est déroulée de janvier 2021 à décembre 2024 au sein du laboratoire Hubert Curien de l'Université Jean-Monnet de Saint-Étienne et du Centre Microélectronique de Provence de Mines de Saint-Étienne à Gardanne.

## Chapitre 2

# Notions préliminaires

## Table des matières

---

|       |                                       |    |

|-------|---------------------------------------|----|

| 2.1   | Introduction                          | 8  |

| 2.2   | Technologie MOS                       | 8  |

| 2.3   | Mémoires volatiles                    | 9  |

| 2.4   | Mémoires non volatiles                | 10 |

| 2.4.1 | Transistor à grille flottante         | 11 |

| 2.4.2 | Mémoires Flash                        | 15 |

| 2.5   | Chiffrement AES                       | 16 |

| 2.6   | Attaques par injection de fautes      | 19 |

| 2.6.1 | Classification des fautes matérielles | 20 |

| 2.6.2 | Modèle de fautes                      | 20 |

| 2.6.3 | Conséquences au niveau de la mémoire  | 21 |

| 2.7   | Scénarios d'attaque                   | 22 |

| 2.8   | Mécanisme de protection               | 26 |

---

## 2.1 Introduction

Ce chapitre décrit quelques notions préliminaires nécessaires à la compréhension des travaux décrit dans cette thèse. Le fonctionnement de la technologie MOS, des mémoires volatiles et non-volatiles, du chiffrement AES ainsi que les notions d'attaque en fautes, de schéma d'attaque et les mécanismes de protection associés seront abordés. Un lecteur familier de ces notions peut s'affranchir de la lecture de ce chapitre.

## 2.2 Technologie MOS

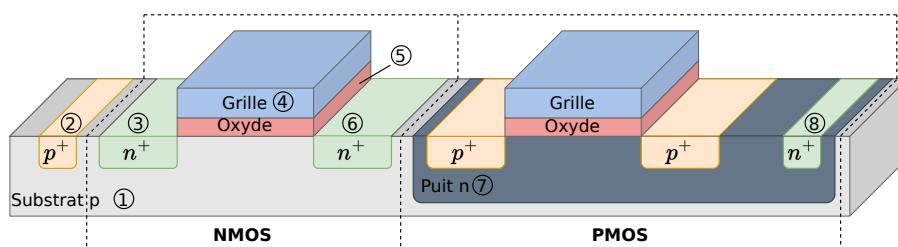

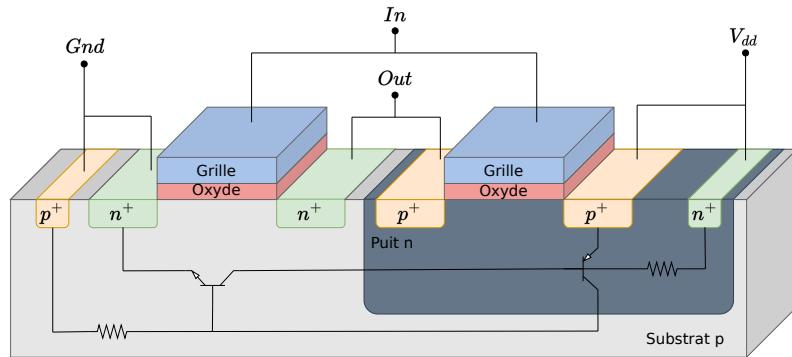

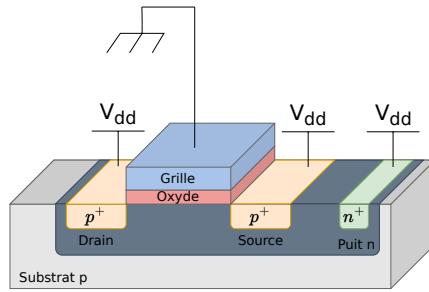

Le transistor *Metal Oxide Semiconductor* (MOS) ou MOSFET est le composant élémentaire des circuits électroniques en technologie Complementary Metal-Oxide-Semiconductors (CMOS). Il est composé d'un empilement Métal | Oxyde | Semi-conducteur et de trois contacts dits de source, de drain et de grille. Il existe deux types de transistors en technologie CMOS [Abb20].

**Transistor NMOS** Il est constitué de deux zones enrichies en électrons (dopage n+) dans un substrat appauvri en électrons (substrat p). Le substrat est généralement polarisé à la masse.

**Transistor PMOS** Il est constitué de deux zones appauvries en électrons (dopage p+) dans un puits enrichi en électron (dopage n). Le puits est habituellement polarisé à la tension d'alimentation. Ce puits est implanté dans le même substrat que les transistors NMOS.

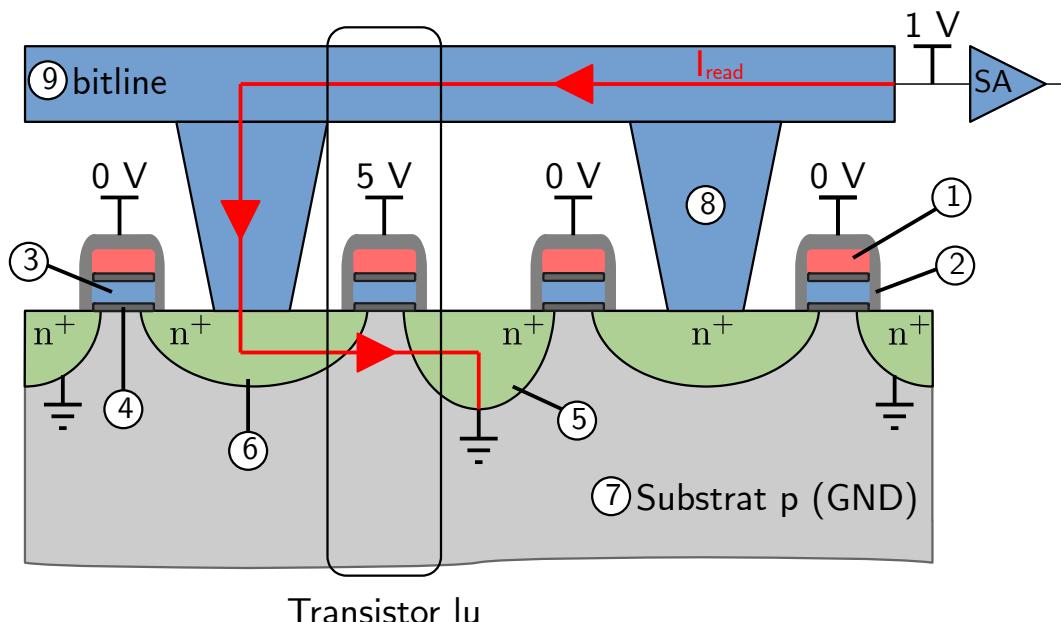

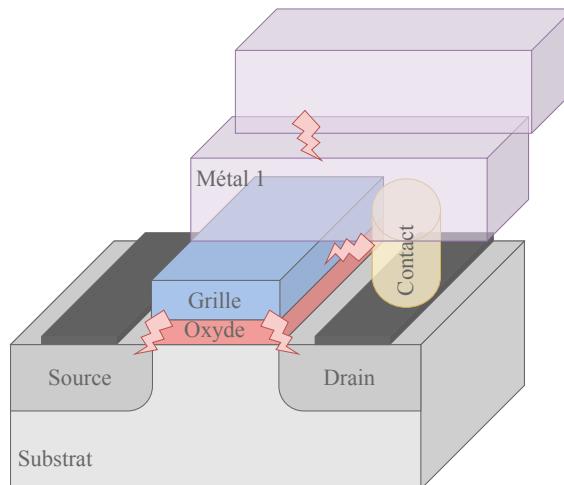

Une vue en coupe de ces deux types de transistors est visible sur la Figure 2.1. On y retrouve le substrat p ① avec son point de polarisation ②, la source du NMOS ③, la grille du NMOS ④, l'oxyde de grille du NMOS ⑤, le drain du NMOS ⑥, le puits n ⑦ et son point de polarisation ⑧.

Figure 2.1 – Vue en coupe de transistors NMOS et PMOS en technologie CMOS.

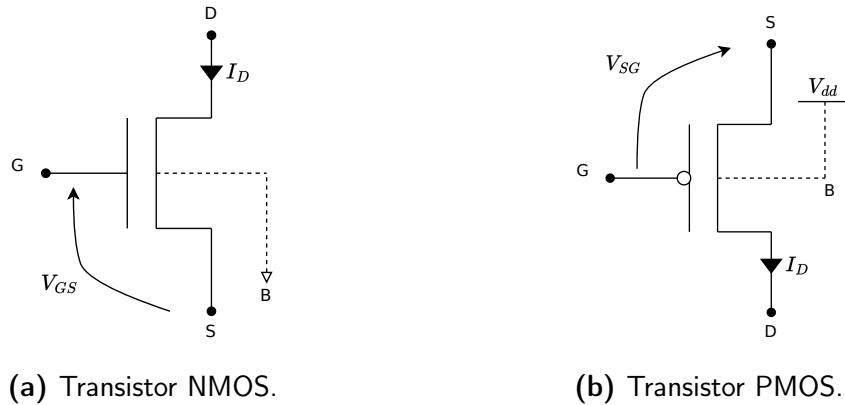

Ces deux types de composants ont quatre terminaux : la grille G, la source S, le drain D et le substrat B (*bulk* en anglais). La figure Figure 2.2 montre la représentation électrique de ces composants.

Figure 2.2 – Schéma électrique des transistors NMOS et PMOS.

Ces composants possèdent deux principaux modes de fonctionnement en saturation : bloqué ou passant.

**Mode bloqué** Le transistor est dit *bloqué* lorsque, en l'absence de polarisation, les différences de dopage entre les zones de diffusion et le substrat sont telles que la source et le drain sont isolés électriquement. Dans ce cas, aucun courant ne peut circuler entre ces terminaux.

**Mode passant** Le transistor est dit *passant* lorsqu'une tension supérieure à la tension de seuil  $V_{th}$  est appliquée sur la grille du transistor. Dans ce cas, un canal de conduction se forme entre la source et le drain à l'interface entre le substrat et l'oxyde de grille. Un courant peut alors circuler entre la source et le drain.

## 2.3 Mémoires volatiles

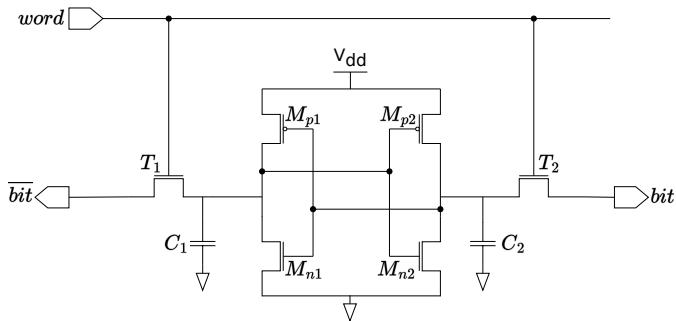

Les mémoires volatiles sont utilisées pour stocker les données, le contexte et les résultats de l'exécution d'un programme. Elles sont donc des cibles privilégiées pour un attaquant. Les données stockées sont conservées tant que le circuit est alimenté. Les mémoires à base de cellules SRAM (*Static Random Access Memory*) sont un type de mémoires volatiles.

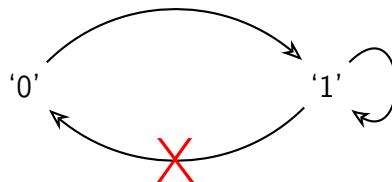

La plus commune des cellules SRAM est constituée d'un circuit bistable, c'est-à-dire qui possède deux états d'équilibre qui représentent respectivement l'état '1' et l'état '0'. Il faut appliquer une stimulation électrique pour forcer la cellule à entrer dans l'un des

deux états. L'équilibre de la cellule est maintenu en l'absence de stimulation extérieure. Chaque cellule stocke un bit d'information.

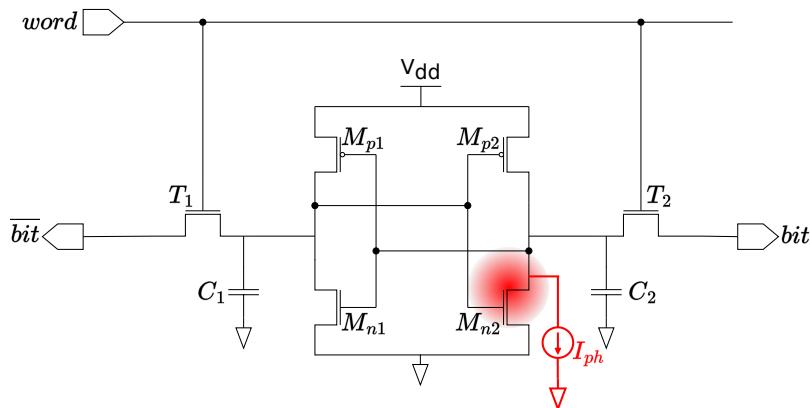

La Figure 2.3 représente une cellule SRAM standard à six transistors. Elle est constituée de deux inverseurs ( $M_{n1}/M_{p1}$  et  $M_{n2}/M_{p2}$ ) connectés tête-bêche et de deux transistors d'accès ( $T_1$  et  $T_2$ ). Ces derniers sont activés par le signal `word` et permettent alors d'accéder au bit d'information via les signaux `bit` et son complémentaire  $\overline{\text{bit}}$ .

Figure 2.3 – Cellule SRAM standard à 6 transistors.

Si l'entrée de l'inverseur  $M_{n1}/M_{p1}$  est à l'état haut ('1'), la capacité de sortie  $C_1$  est maintenue déchargée ('0') par le transistor  $M_{n1}$  qui est passant. À l'inverse, si l'entrée de l'inverseur  $M_{n2}/M_{p2}$  est à l'état bas ('0'), la capacité de sortie  $C_2$  est maintenue chargée ('1') par le transistor  $M_{p2}$  qui est passant.

La lecture du point mémoire se fait en activant la ligne `word`, cela rend les transistors d'accès  $T_1$  et  $T_2$  passants. La donnée est donc disponible sur le signal `bit` et son complémentaire  $\overline{\text{bit}}$ . L'écriture d'un '0' (respectivement d'un '1') dans la cellule se fait en activant les signaux `word` et `bit` et en désactivant le signal  $\overline{\text{bit}}$  (respectivement en activant les signaux `word` et  $\overline{\text{bit}}$  et en désactivant le signal `bit`).

## 2.4 Mémoires non volatiles

Une mémoire non-volatile est une mémoire qui conserve les données stockées en l'absence d'alimentation électrique. Il en existe trois principaux types : EPROM (*Erasable Programmable Read-Only Memory*), EEPROM (*Electrically Erasable Programmable Read-Only Memory*) et Flash. Historiquement, les premières mémoires non-volatiles à voir le jour sont les mémoires EPROM. Elles peuvent être lues et programmées, mais ne sont pas effaçables électriquement. L'effacement des mémoires EPROM est effectué en exposant la puce à une lumière UV au travers d'une fenêtre en quartz. Les mémoires EEPROM sont une évolution des mémoires EPROM. Elles sont effaçables électriquement sans qu'il soit nécessaire de retirer la mémoire de la puce de l'appareil. Les mémoires Flash sont un type de mémoire EEPROM qui se distingue par leur rapidité et leur effaçabilité par

secteur, et non par adresse individuelle. Les technologies EPROM et EEPROM sont aujourd'hui obsolètes.

Elles sont toutes construites autour d'un composant élémentaire : le transistor à grille flottante.

### 2.4.1 Transistor à grille flottante

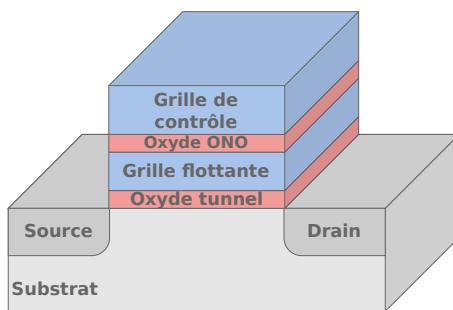

Un transistor à grille flottante en technologie Flash possède la même structure qu'un transistor MOS à l'exception de la grille flottante qui est ajoutée dans l'oxyde entre le substrat et la grille de contrôle. Cette grille flottante est isolée électriquement du reste de la structure. Une représentation schématique d'un transistor à grille flottante est visible en [Figure 2.4](#).

**Figure 2.4 – Vue en coupe d'un transistor à grille flottante.**

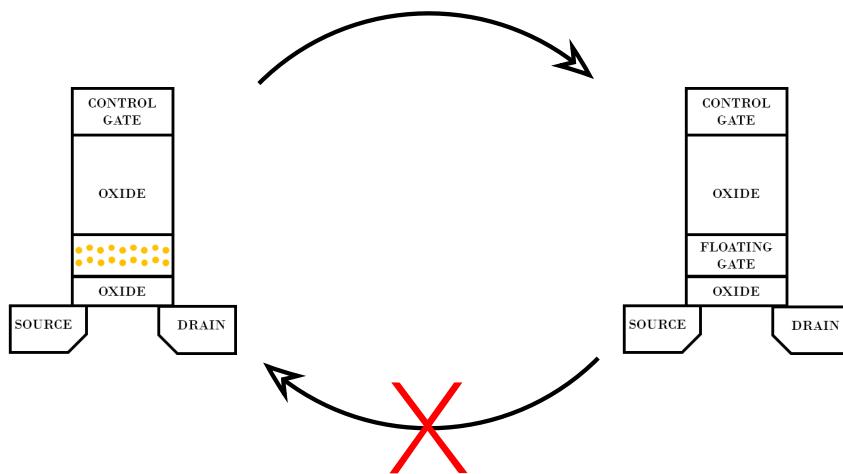

La grille flottante est utilisée pour stocker une charge électrique. La présence de cette charge électrique traduit l'état, effacé ou programmé, du transistor à grille flottante. Cet état permet de représenter un bit d'information. Selon la convention usuelle adoptée par une majorité des fabricants de semi-conducteurs, l'état effacé (absence d'électrons dans la grille flottante) correspond à un '1' logique et l'état programmé (présence d'électrons dans la grille flottante) correspond à un '0' logique.

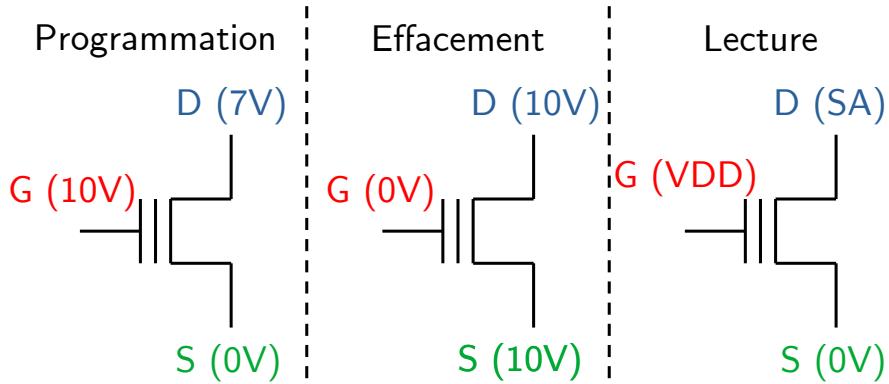

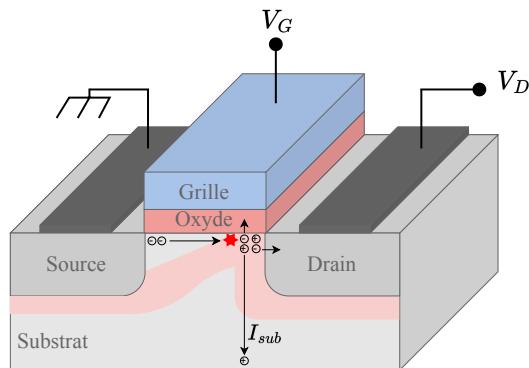

Il existe trois types d'opérations au sein des mémoires Flash : (i) la programmation, (ii) l'effacement et (iii) la lecture. La [Figure 2.5](#) synthétise les différentes tensions aux bornes d'un transistor à grille flottante pour les opérations d'écriture, d'effacement ou de lecture. Les valeurs sont données à titre d'exemple et peuvent varier d'un composant à l'autre en fonction de la technologie employée. La programmation et l'effacement consistent en l'ajout ou le retrait de charges électriques, des électrons, dans la grille flottante. Deux principaux mécanismes permettent ces opérations :

1. **L'injection d'électrons chauds** permet la programmation des transistors à grille flottante. Un potentiel est appliqué sur la grille de contrôle et sur le drain alors que

Figure 2.5 – Tensions appliqués aux bornes d'un transistor à grille flottante pendant les différentes opérations [Vie+21].

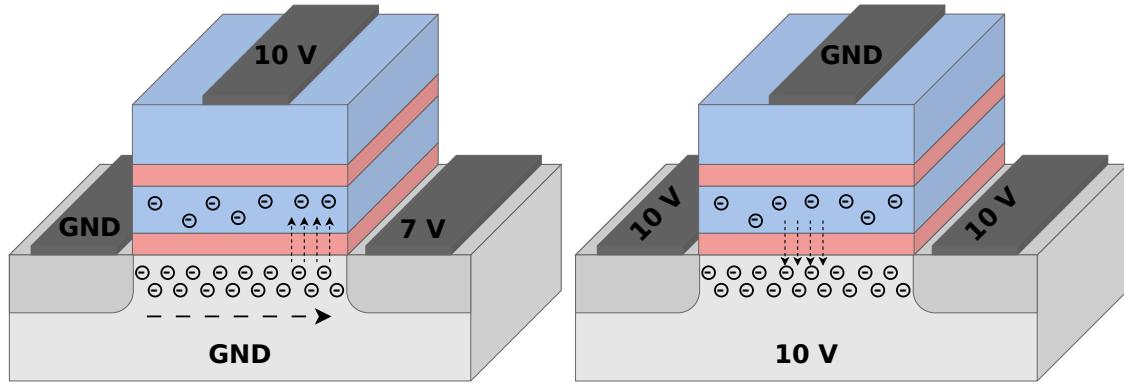

la source est maintenue à la masse. Un champ électrique important apparaît donc dans la zone de charges d'espace, un courant électrique circule entre la source et le drain, les électrons constituant ce courant ont assez d'énergie pour passer la barrière de potentiel représentée par l'oxyde tunnel et sont injectés dans la grille flottante. La Figure 2.6a illustre ce phénomène.

2. L'effet tunnel Fowler-Nordheim est utilisé pour l'effacement des transistors à grille flottante. Un champ électrique important est appliqué entre le substrat et la grille de contrôle alors que la source et le drain sont en haute impédance. Les électrons stockés dans la grille sont ainsi capables de traverser l'oxyde tunnel par effet tunnel pour rejoindre le substrat. La Figure 2.6b illustre ce phénomène.

(a) Mécanisme d'injection d'électrons chauds. (b) Effet tunnel Fowler-Nordheim.

Figure 2.6 – Programmation (a) et Effacement (b) d'un transistor à grille flottante.

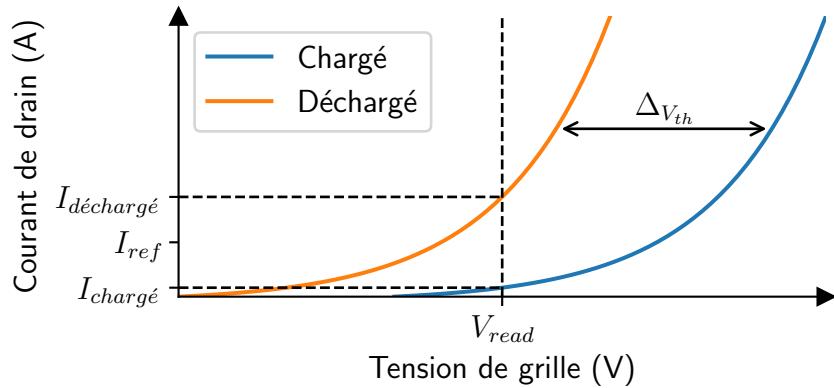

La présence des charges électriques dans la grille flottante génère une augmentation de la tension de seuil  $V_{th}$  du transistor à grille flottante comme le montre la Figure 2.7. Pour une certaine tension  $V_{read}$  appliquée sur la grille de contrôle, le transistor à grille flottante va créer un appel de courant différent selon la charge stockée dans la grille

flottante, c'est-à-dire selon  $V_{th}$ . Ainsi, l'état logique du transistor à grille flottante est déterminé par la présence de charges dans celle-ci, ce qui affecte la tension de seuil.

Figure 2.7 – Caractéristique I-V de transistors à grille flottante chargé et déchargé.

La lecture d'un transistor à grille flottante est effectuée en appliquant la tension de lecture  $V_{read}$  sur la grille de contrôle, le courant appelé par le transistor est ensuite comparé à un courant de référence  $I_{ref}$  par un comparateur de courants (ou *sense amplifier* en anglais). Ce dernier génère un ‘1’ ou un ‘0’ selon la différence de courant mesurée.

Par convention, un transistor chargé, c'est-à-dire avec des électrons dans sa grille flottante, est dit *programmé* et représente l'état logique ‘0’ alors qu'un transistor ne contenant pas d'électrons dans sa grille flottante est dit *effacé* et représente l'état logique ‘1’. La convention inverse peut aussi être rencontrée.

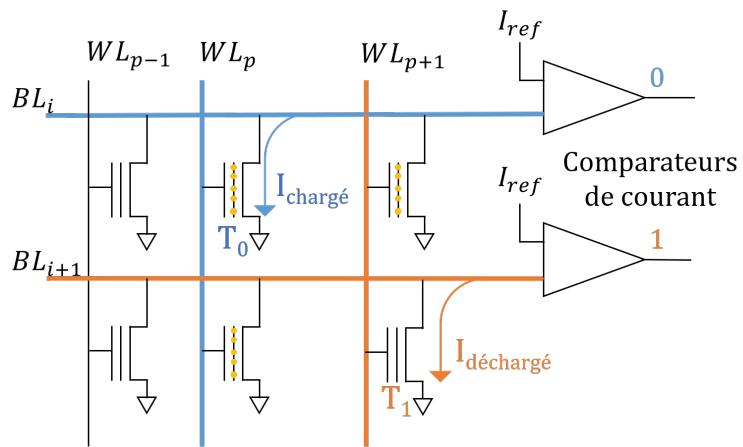

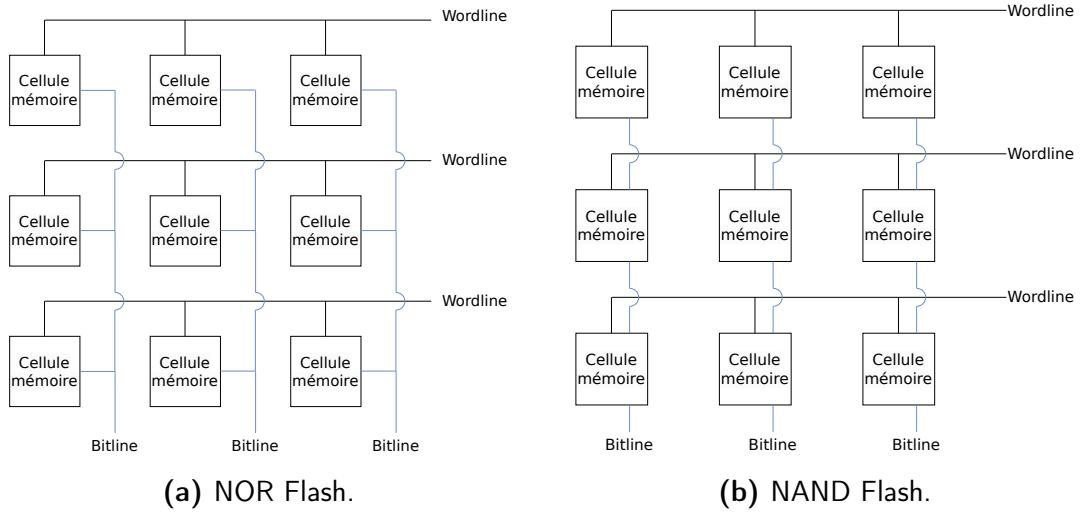

La [Figure 2.8](#) schématise la lecture de transistors à grille flottante programmés et effacés. Ce schéma est valable pour une mémoire Flash respectant l'architecture NOR. L'agencement des transistors est différents pour une mémoire NAND Flash.

Pour lire la valeur stockée dans le transistor  $T_0$  qui est chargé, on applique  $V_{read}$  sur la *wordline*  $WL_p$ . Le transistor à grille flottante  $T_0$  va ainsi appeler un courant  $I_{chargeé}$  qui est inférieur à  $I_{ref}$  ce qui produira un ‘0’ en sortie du comparateur de courant. C'est le scénario bleu sur la [Figure 2.8](#).

Pour lire la valeur stockée dans le transistor  $T_1$  qui est déchargé, on applique  $V_{read}$  sur la *wordline*  $WL_{p+1}$ . Le transistor à grille flottante  $T_1$  va ainsi appeler un courant  $I_{déchargé}$  qui est supérieur à  $I_{ref}$  ce qui produira un ‘1’ en sortie du comparateur de courant. C'est le scénario orange sur la [Figure 2.8](#).

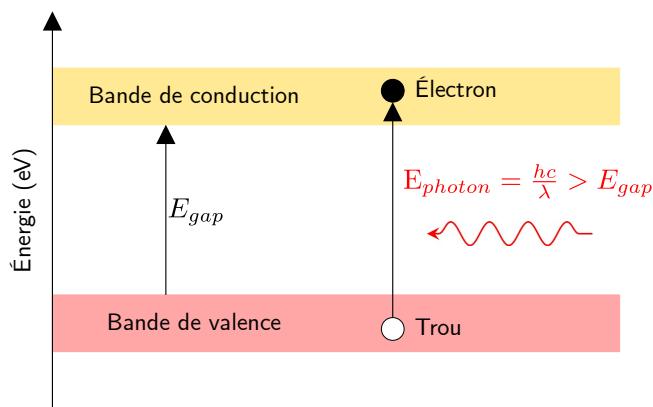

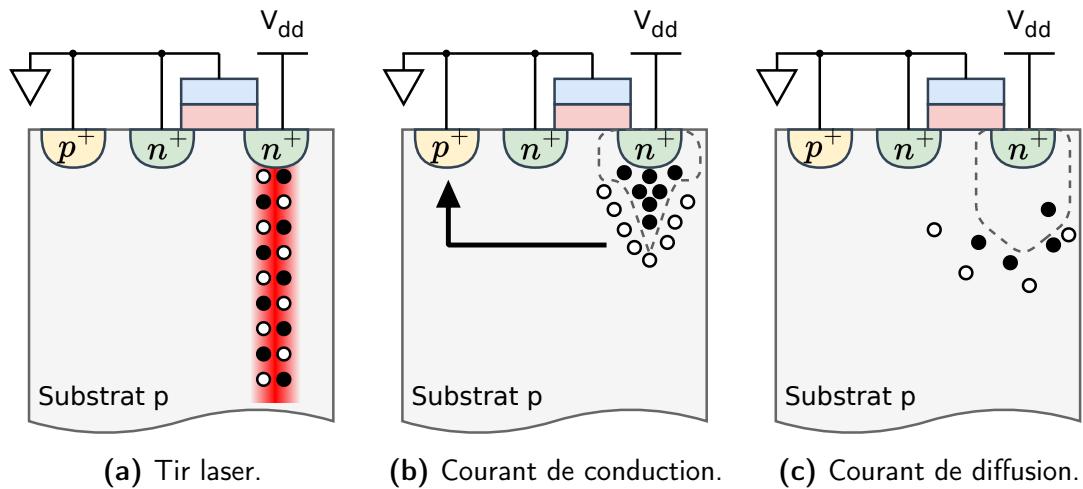

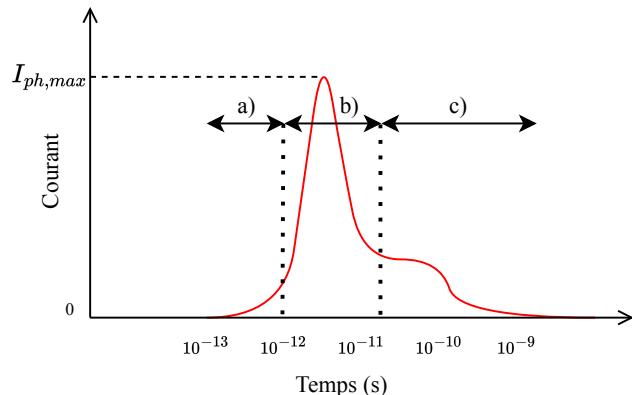

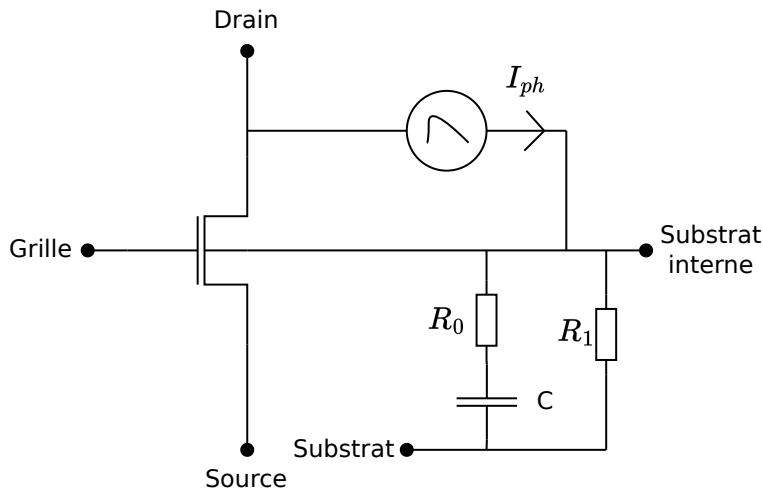

Figure 2.8 – Lecture de transistors à grille flottante (architecture NOR).